芯东西(公众号:aichip001)

作者 | 高歌

编辑 | Panken

芯东西10月12日报道,今天,全球IP、EDA巨头Cadence召开中国区线上用户大会(CadenceLIVE China 2021),Cadence线上用户大会已经举办了17年,本次也吸引了很多巨头厂商参与。Cadence中国区总经理汪晓煜、Cadence CEO陈立武、Cadence总裁Anirudh Devgan等参与了本次大会。

陈立武称,数据正在推动半导体行业发展,仅去年一年全球就有超过100个数据中心开放。由于安全和实时处理等要求,越来越多的人工智能应用正在走向边缘,预计2030年将会有80%的数据在边缘处理。同时,越来越多的系统厂商进入半导体行业,先进节点、先进封装、芯片创企融资、亚太地区市场飞速增长等因素都成为了半导体发展的动力。

Anirudh Devgan则回顾了Cadence智能系统设计战略的芯片、系统和人工智能3级的布局,并分享了Cadence在射频(RF)和计算流体动力学(CFD)等领域的产品与案例。

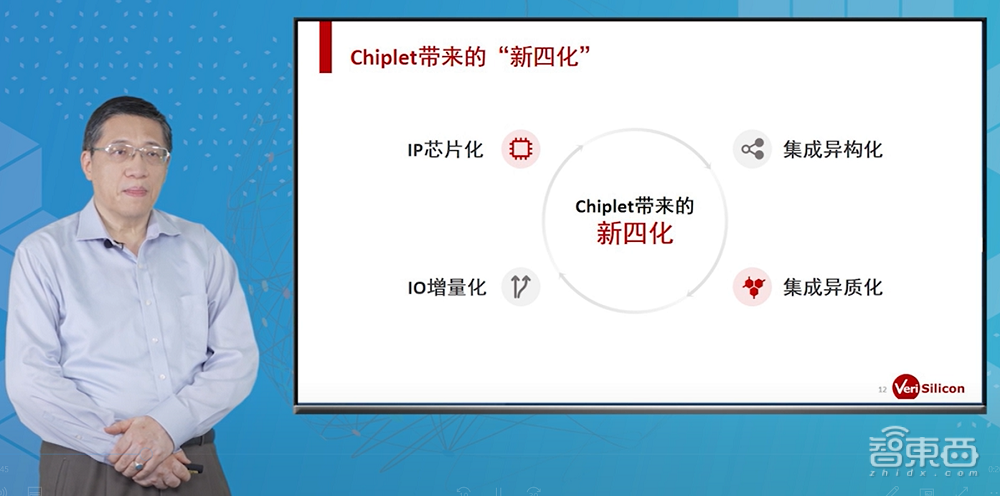

中国IP厂商芯原股份的董事长、总裁兼首席执行官戴伟民也参与了本次会议,分享了Chiplet(芯粒)技术的起源和生态构成,以及这一技术给半导体行业带来的IP芯片化、集成异构化、集成异质化和IO增量化等影响。

一、每年仅有0.5%数据被分析,将成行业发展重要机遇

陈立武从数据角度分析了半导体行业的发展前景。他提到几年前,人们认为半导体发展速度正在放缓。但是如今,以数据为中心的时代正在快速推动各个行业对半导体的需求。

▲Cadence CEO陈立武

▲Cadence CEO陈立武

5G技术正在加速发展,L2\L3级别的自动驾驶正在普及,工业物联网也越来越重要,AI(人工智能)正在影响行业中的一切。

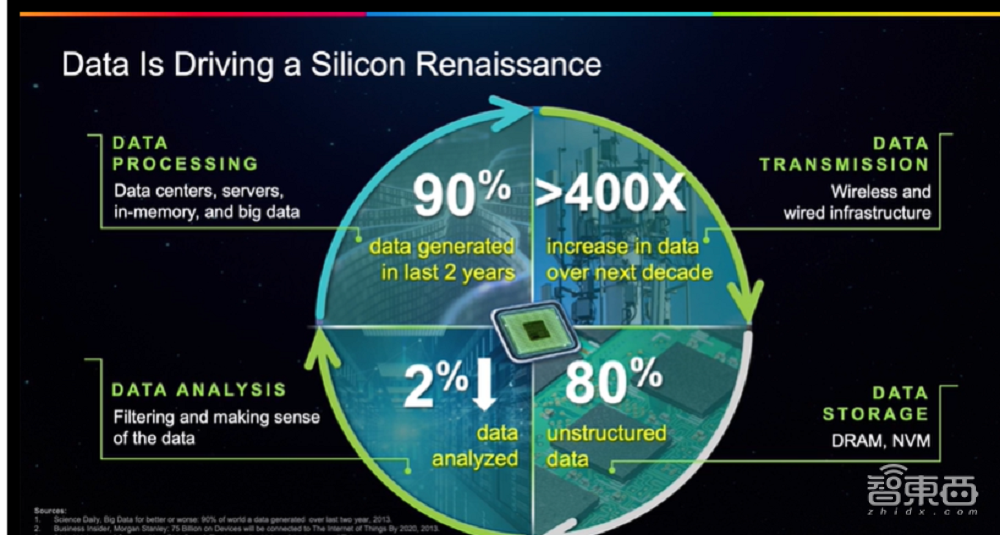

由于各类新兴技术发展,每天都有大量的数据被创建。所有这些数据都需要传输、存储、处理和分析,这也就需要高性能计算、高带宽传输和高密度存储。

为了满足这些需求,半导体行业需要在架构设计、EDA工具、IP、制造等各个领域进行大量创新。

目前90%的数据都是在过去两年内生成的,80%的数据是非结构化的,如图形视频等。虽然数据很多,但是目前每年仅有2%的数据会被分析。由于分析也会产生数据,接下来的5年里,实际被分析的数据比例将会变为0.5%。

据估计,去年全球的超级数据中心支出超过1200亿美元,仅去年一年就有超过100个数据中心开放,这些数据中心参与了数据周期的所有阶段,推动了计算、存储和网络技术的创新。

同时,越来越多的人开始转向软件定义存储、网络,软件开始定义硬件。超级计算机也在推动行业走向定制化芯片设计,以满足差异化需求和最佳的用户体验。

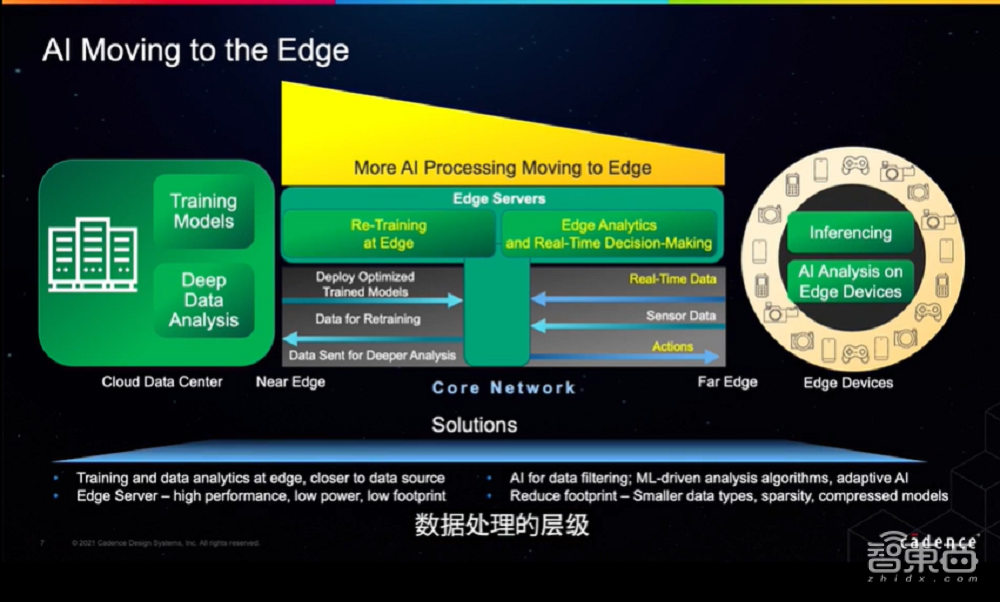

陈立武说,人工智能也对几乎每个行业带来了巨大的变革,但当前仍处于非常初级的阶段。通过云计算,数据也可以被深入地进行分析,但这带来了一些问题。

首先是数据隐私,银行、医疗等数据都是非常敏感的数据,需要谨慎处理。其次把大量数据发送到云是不现实的,这将消耗巨大的带宽,其发送和获取信息延迟将还会太高。

因此,实时处理问题的人工智能应用正在越来越多地走向边缘。这些应用在边缘进行分析,以实施决策,将对自动驾驶等领域产生积极意义。目前,仅有20%的数据在边缘进行处理,而到2030年这一比例将会变为80%。

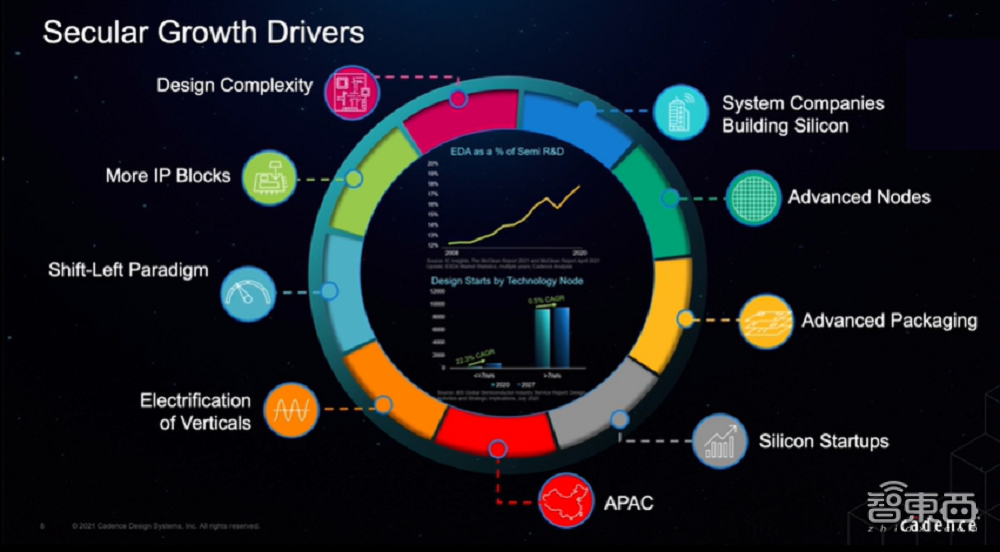

此外,系统厂商进入半导体、先进节点、先进封装、芯片创企、亚太地区市场等因素也在推动半导体行业快速发展。

而随着制程工艺的发展,EDA领域的研发投入大幅增加,推动了Cadence等厂商的战略。Cadence的研发投入占营收比例已达40%。

二、解析3大重要新品,Cerebrus可降低15%功耗

本次大会,Cadence总裁Anirudh Devgan等人分享了Integrity 3D-IC平台、Helium Virtual及Hybrid Studio平台和Cerebrus机器学习设计工具3个新产品。

Integrity 3D-IC平台是业界首个集成系统级和SoC级的解决方案,支持electrothermal analysis(电热分析)、多die STA和系统级物理仿真验证。

Helium Virtual C++ SoC模型允许软件开发和RTL设计并行运行,该模型运行速度比RTL快数百或数千倍,这使得其硬件/软件集成和调试比RTL模型更高效。当前,Helium Virtual and Hybrid Studio平台已经上市。

Cerebrus是一款基于机器学习(ML)的设计工具,可同时优化设计中的多个步骤,可将生产力提升10倍。瑞萨电子和三星电子的团队表达了自己对Cerebrus的看法。

瑞萨电子数字设计技术部门负责人Satoshi Shibatani称,瑞萨电子在12nm高速CPU设计项目中应用了Cerebrus,其不仅可以优化物理实现流程,还可以优化布局规划。在50次运算过后,其生成了新的设计流程和布局规划,将这款CPU性能提升了10%以上,节省了数个月工程师手动布局时间。

在最新的4nm和6nm节电设计上,三星电子的晶圆厂团队运用了Cerebrus工具。该工具可以很容易地配置,优化代码,为线宽、层架间距、过孔类型等网格配置设计优化方案。和手动设计相比,Cerebrus在4nm节点的供电线路设计上提升了50%的时序(timing),并优化了功耗。

三、Cadence智能系统设计战略:布局芯片、系统和普适智能

Anirudh Devgan也对Cadence在2021年的战略和发展情况做了总结。

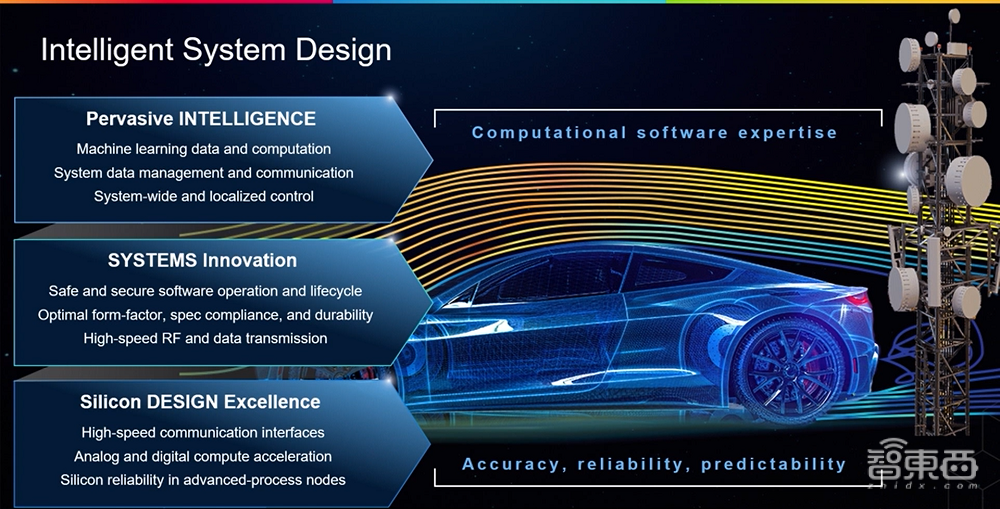

他提到当前快速演进的智能系统设计备受行业关注,其智能系统共有3层。以汽车为例,汽车电子设计分为三个领域,其核心是系统级的芯片,第二个是系统和软件堆栈,第三个则是汽车周身的数据和普适智能。

这样的智能系统设计3层也会出现在智能手机、数据中心等多个领域,这也就是Cadence智能系统设计战略。其核心为EDA和IP;之后是系统设计,Cadence在3D-IC、系统仿真、嵌入式软件、软件启动等领域进行了很多布局与投资,是Cadence战略的重要组成部分;第三层则是人工智能以及与人工智能相关的整个数据分析。

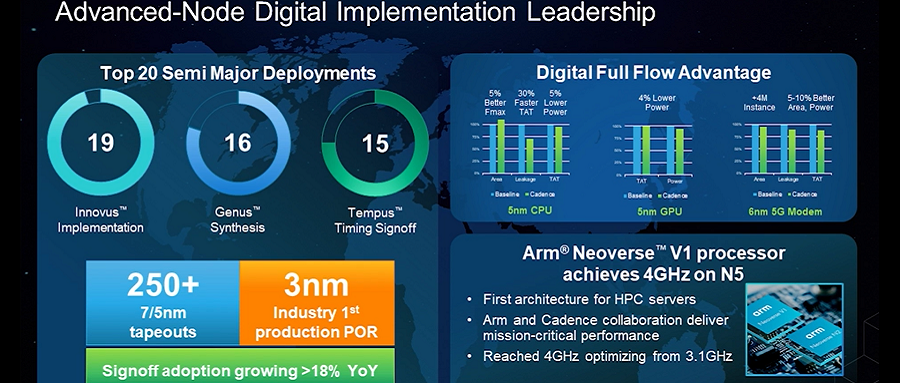

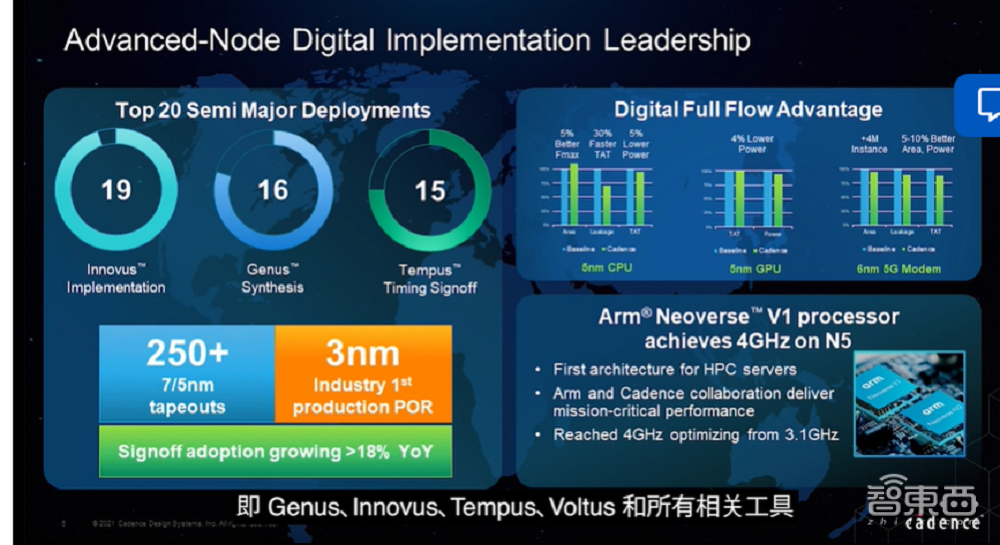

Anirudh Devgan称,在数字设计领域,Cadence的各类产品都取得了很好的成绩。比如Innovus Implementation被前20大半导体公司中的19家使用,Genus Synthesis被前20大半导体公司中的16家使用,Tenpus Timing Signoff则被前20大半导体公司中的15家采用。Cadence也和Arm一起,在台积电N5工艺节点上实现了4GHz成果。

在硬件平台方面,Cadence今年推出了Palladium Z2和Protium X2平台。

AMD的Alex Star称,相比于Palladium Z1,Palladium Z2的工作负载吞吐量显著提高,能够快速、容易地从仿真平台转变为高速的企业级原型设计平台。英伟达的Narendra Konda谈道,通过Palladium Z2和Protium X2,将一个数亿个晶体管的设计进行编译、创建仿真模型并放入仿真平台中仅需4个小时,而此前该过程需要48甚至72个小时。

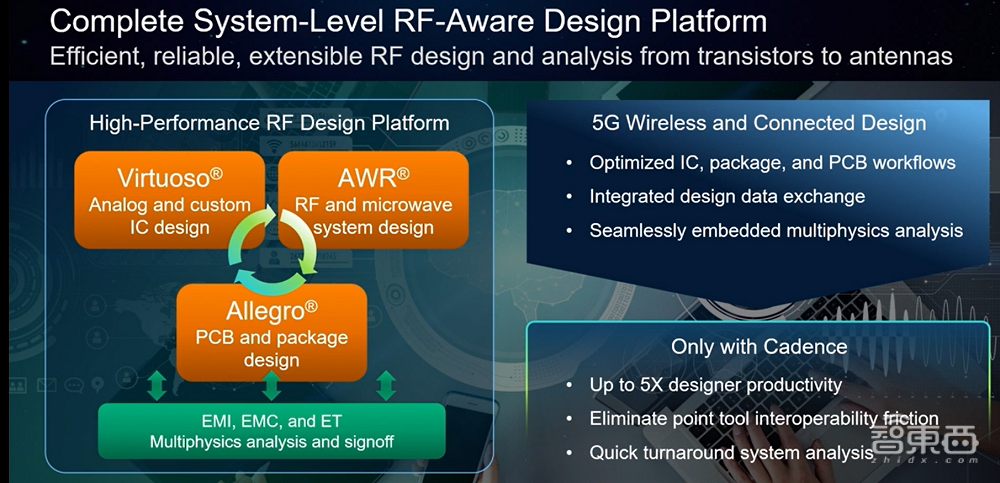

在系统层面,Anirudh Devgan回顾了Cadence在射频(RF)领域的进展。一年以前,Cadence收购了National Instrument的射频平台AWR,并将该平台与Virtuoso和Allegro集成在一起,形成了完整的射频解决方案,可提供5倍的射频设计效率。

美国创企Metawave的创始人兼CEO Maha Achour称,Cadence射频设计、分析平台使得他们可以与大公司进行竞争,完成了其5G高频毫米波频段雷达。

在计算流体动力学(CFD)领域,Cadence也进行了多次收购和布局,如拥有Omnis平台的CFD厂商NUMECA、网格划分领域常熟Pointwise等。

在航海方面,新西兰的帆船设计团队Emirates Team称其CFD工具对其设计至关重要。在第36届美洲杯帆船赛上,他们需要采用一种新的单体帆船,并且只被允许建造一艘船。最终,因为Cadence旗下的CFD工具,该团队成功实现了船体建造和细节优化。

此外,Cadence还有Clarity这一有限元电磁求解器来帮助在CFD领域进行分析。而Clarity 3D Solver可以进行快速、准确的3D分析,能够缩短设计周期并快速将产品推入市场。该产品还可以同时运行数千个CPU进行数据处理。

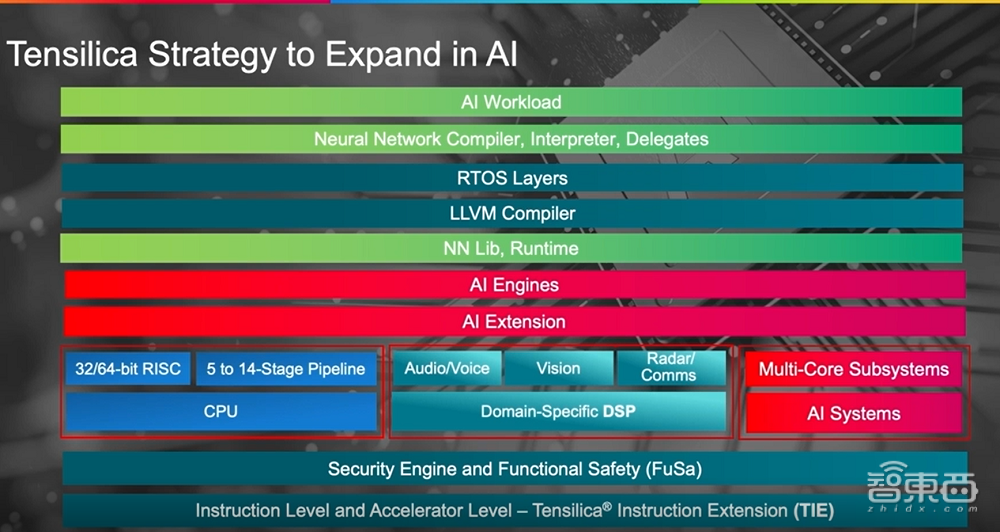

在封装领域,Cadence有Allegro封装和PCB设计平台,该平台是使用最广泛的高级封装解决方案。在人工智能层面,Cadence将AI Extension加入到了处理器管线中,并正在研发基于其sparks计算技术的AI引擎。该引擎和管线、嵌入式CPU结合,将能够提供更强大的AI性能。

四、Chiplet维系摩尔定律,芯原股份:IP即芯粒

芯原股份创始人、董事长兼CEO戴伟民则回顾了Chiplet(芯粒)生态的建立。

在1958年杰克·基尔比发明了集成电路,之后英特尔创始人戈登·摩尔预言:“集成电路上的器件数量每个十八个月将翻一番。”这就是摩尔定律的诞生。

随着芯片特征线宽的下降,互连延迟(interconnect delays)对设计的影响越来越大,芯片性能提升越来越难。但换一种思路来看,更小的裸片带来了更高的硅利用率和产能。所以Chiplet通过多种集成,使系统空间内的密度持续增长。研究机构预计,2035年,Chiplet市场规模将达到570亿美元。

戴伟民称,Chiplet给半导体行业带来了IP芯片化、集成异构化、集成异质化和IO增量化等影响。

具体来说,2015年,Marvell创始人周秀文在ISSCC 2015上提出了MoChi(模块化芯片)架构概念。AMD则是最早将Chiplet应用于商业产品,平衡了自身成本、性能和功耗。

随后,英特尔也快速采用Chiplet技术,并免费提供了AIB总线接口许可,以支持Chiplet生态建设。2018年,英特尔将EMIB(嵌入式多硅片)技术升级为逻辑晶圆3D堆叠技术。2019年,英特尔推出Co-EMIB技术,能够将两个或多个Foveros芯片互连。

2.5D和3D封装技术的发展也推动了Chiplet生态的建立。2020年6月,英特尔正式发布Lakefield芯片,这是首款基于Foveros 3D立体封装技术的芯片,采用1个大核+4个小核的混合CPU设计。

在最近的英特尔架构日上,其提出了下一代可扩展处理器Sapphire Rapids架构创新。英特尔还提出了超异构计算的技术愿景。

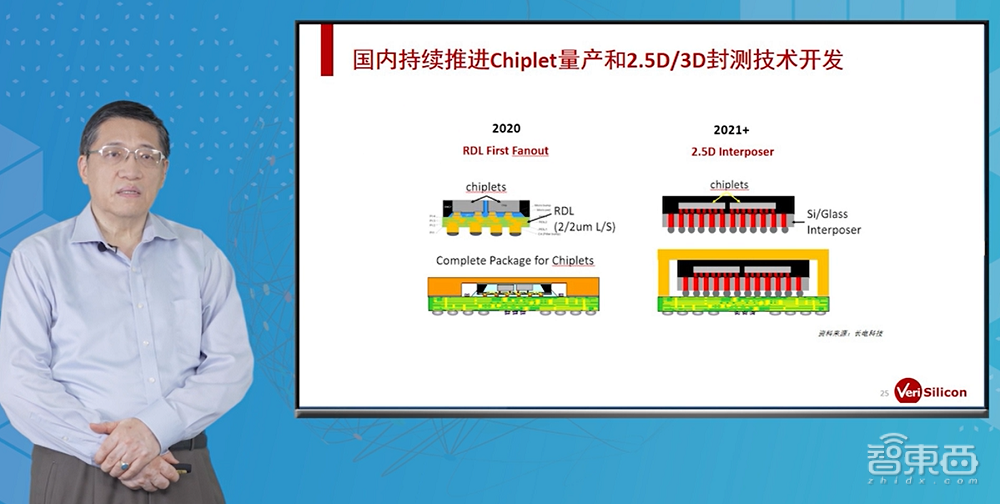

除了英特尔,台积电提出了2.5D CoWoS封装技术和3D SoIC封装技术;三星则提出了3D封装技术X-Cube。国内厂商如长电科技也在持续推进Chiplet技术的开发。

在接口方面,2018年7家公司成立ODSA(开放专用域架构)组织,制定Chiplet开放标准、促进Chiplet生态、催生低成本SoC替代方案。目前,该组织会员已超过50家。

2019年,英特尔携手阿里巴巴、思科、戴尔、Facebook、谷歌、HPE、华为以及微软成立Compute Express Link(CXL)开放合作联盟,实现CPU与GPU、FPGA等专用加速器之间的高速、高效互连。

而Chiplet给产业带来了一个重要变化就是IP芯片化(IaaC),IP也是芯原股份的重要业务。

芯原股份成立于2001年,今年已成立20年。当前芯原股份接近50%的营收在国外,但是其95%的研发人员都在国内。根据研究机构数据,芯原是中国大陆排名第一、全球第七的IP供应商,具备丰富的IP储备。

此外,戴伟民提及,芯原股份在视频处理器(VPU)、神经网络处理器IP(NPU)、图形处理器(GPU)、数字信号处理器(DSP)、图像信号处理器(ISP)和显示处理器(Display Processor)等领域均有相应的产品和布局。

在IP芯片化的驱使下,芯原股份提出了IP即芯粒(IaaC)的理念,旨在实现特殊功能IP的“即插即用”。目前,芯原股份推出了多种IP的子系统解决方案FLEXA API。

在芯片平台化方面,芯原股份能够提供一站式设计服务,全球首批7nm EUV芯片流片一次成功,已开发5nm芯片。通过Chiplet技术,芯原股份可以在自动驾驶等领域快速进行迭代。

结语:软件定义硬件,Cadence大会展现行业趋势

Cadence作为行业内头部的EDA和IP厂商,每年Cadence的用户大会都会吸引不少的行业目光,其战略布局对于半导体行业发展有着比较重要的参考价值。

本次,Cadence总裁Anirudh Devgan详细解析了其智能系统设计战略,以及Cadence在射频、计算流体动力学和完整封装、设计等领域的产品情况,这些也是行业的重要应用领域。如今云计算和人工智能已成为EDA领域的两大重要趋势,而软件正在重新定义硬件,影响行业发展。