芯东西(ID:aichip001)

作者 | 温淑

编辑 | Panken

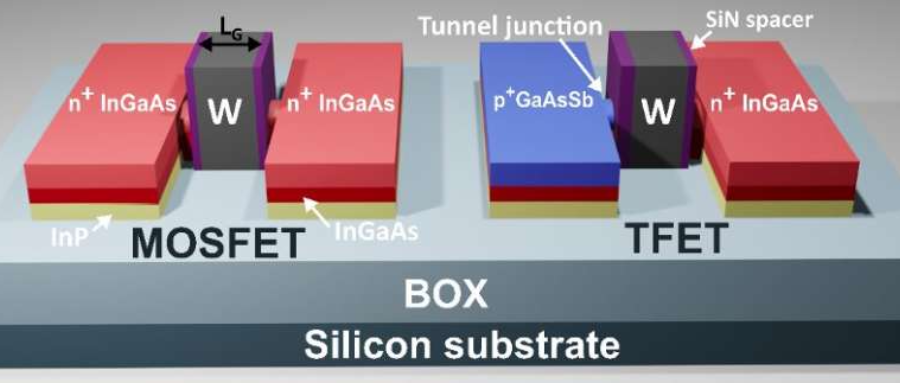

芯东西3月11日消息,近日,IBM欧洲研究中心和洛桑联邦理工学院的研究人员研发出一种混合硅基器件。该器件结合了三五族场效应晶体管和金氧半场效晶体管的优势,能够在不同电压条件下实现较低的功耗,未来或可用于减少信通行业的碳足迹。

这项研究已发表于国际学术期刊《自然–电子学》,论文名称为《集成在硅上的混合三五族场效应晶体管和金氧半场效晶体管技术平台(A hybrid III–V tunnel FET and MOSFET technology platform integrated on silicon)》。

论文链接:https://www.nature.com/articles/s41928-020-00531-3

一、两种场效应管性能各有优劣

摩尔定律决定了,缩小晶体管的尺寸成为全球半导体行业共同追逐的目标。但是,IBM欧洲研究中心和洛桑联邦理工学院的研究人员认为,在缩减晶体管尺寸以外,还有其他提升晶体管性能的方法。

研究人员注意到,金属氧化物半导体场效应晶体管(MOSFET)和隧道场效应晶体管(TFET)这两种晶体管,具备着“互补”的性能特点。

具体来说,MOSFET作为应用最为广泛的晶体管之一,其主要缺陷在于能耗过高。这是因为MOSFET不能在降低电压供应的同时限制断态漏电流(off-state leakage current)。

相比之下,TFET可以利用量子力学隧穿(quantum mechanical tunneling)来克服这一缺陷。其中,在环境温度下,三五族异质结的TFET(III–V TFET,混合三五族场效应晶体管)仅需不到60 mV的栅极电压摆幅,就可使漏电流发生数量级的变化。要注意的是,尽管TFET功耗较低,其在较高的驱动电压下的速度和能效无法达到MOSFET的水平。

基于此,研究人员致力于结合MOSFET和III–V TFET,从而创造出兼具两种场效应管优势的器件。

二、首个基于两种场效应管的混合硅基器件

研究人员分享了对这款硅基混合器件的具体设计思路:在较低电压水平下,TFET提供较低的泄露和良好的性能表现;(较高电压水平下)在相同尺寸和偏差(bias)下,MOSFET更快,并提供更好的电流驱动。

最终,研究团队开发出一款混合硅基器件。基于该器件,用户可实现混合逻辑块,以适应不同类型设备的不同特性。

由于能够在不同驱动电压下到达较优的功耗水平,这种新型器件或可用于研发节能电子产品。研究团队成员之一Clarissa Convertino称:“这种低功耗技术平台为未来节能电子产品铺平了道路,最终目标是减少信息和通信行业的碳足迹。”

根据初步评估结果,该器件能够使TFET实现42 mV dec−1的最小阈下斜率(minimum subthreshold slope)、使MOSFET实现62 mV dec−1的最小亚阈值斜率。

Clarissa Convertino向外媒Tech Xplore表示:“我们展示了首个MOSFET和III–V TFET的混合技术平台,(这项技术)具有可扩展的工艺,适于进行大规模半导体生产。”

三、灵活适应工作环境背后技术揭秘

这款新型混合硅基器件如何灵活适应不同的工作条件?根据Tech Xplore报道,研究人员为该器件引入了一个“自对准的源更换步骤(self-aligned source-replacement step)”。

在该技术平台上,GaAsSb源的位置通过数字刻蚀(digital etching)来确定。数字刻蚀是一个在纳米尺度去除材料的过程。

另外,除了单一的掩模和外延步骤,用于开发新型器件的两款场效应管完全相同。

Clarissa Convertino称,研究团队还将探索研发其他工作条件下的超低功耗器件。“在我们的下一步研究中,我们将进一步探索开发平台的潜力及其在不同工作条件下的应用,例如在低温甚至是毫开尔文状态下。”她说道。

结语:新型器件仍待市场检验

追求更高性能、更低功耗是半导体器件设计过程中永恒的追求。但随着摩尔定律发展,晶体管尺寸逐渐逼近物理极限。

这一背景下,通过创新材料、创新架构等各种方式创造出性能优异的器件,成为全球半导体产学界的努力方向之一。

本项研究通过创新地结合两种不同场效应管,研发出适应不同电压条件的低功耗混合器件。尽管仍待市场检验,该技术亦不失为一种成功的尝试。

来源:Tech Xplore