芯东西(公众号:aichip001)

作者 | 高歌

编辑 | Panken

芯东西10月8日报道,在本周刚刚举行的第五届三星晶圆代工年度论坛(Samsung Foundry Forum 2021)上,三星电子总裁兼代工业务负责人Siyoung Choi公布了有关3/2nm GAA晶体管量产计划、三星RF射频平台和其在美建厂的情况。

Siyoung Choi宣布,三星首批3nm芯片将于2022年上半年开始生产,而2nm工艺节点将于2025年进入量产。在本次活动上,三星电子还首次推出了17nm FinFET专业工艺技术,该工艺比28nm工艺性能提升了39%,功率效率提高了49%。以下是芯东西对Siyoung Choi完整演讲的编译、整理。

一、预计2022上半年3nm量产,性能提升30%

在晶圆代工论坛上,Siyoung Choi谈道:“我们将提高整体产能并引领最先进的技术,同时进一步扩大硅片规模并通过应用继续技术创新。”

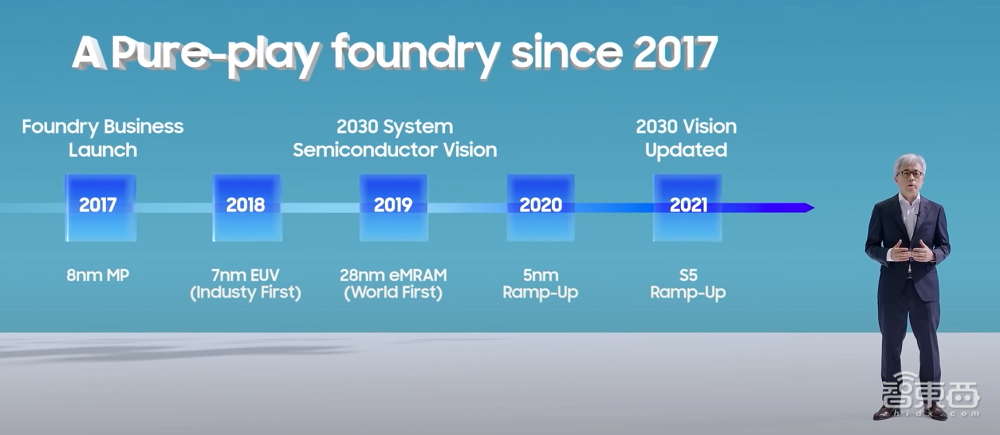

他提到自2017年以来,三星电子的制程工艺每年都有所升级,而三星电子代工业务将加强节点制程多样化、新晶圆厂产能扩张和提升代工服务等领域。

▲三星电子代工产品迭代图

▲三星电子代工产品迭代图

Siyoung Choi宣布,2022年上半年,三星电子将开始生产首批3nm芯片,第二代3nm芯片预计将于2023年开始生产。

三星电子的3nm GAA工艺采用了MBCFET晶体管结构,与5nm工艺相比,其面积减少了35%,性能提高了30%且功耗降低了50%。Siyoung Choi称,随着工艺成熟度的提高,三星电子3nm工艺良率正在接近目前量产的4nm工艺水平。

相比之下,今年6月台积电总裁魏哲家在2021年台积电技术论坛上宣布,其3nm芯片将按计划于2022年下半年开始量产。媒体报道称,苹果和英特尔可能将是首批客户。

此外,Siyoung Choi称,2025年三星电子将推出基于MBCFET的2nm工艺,进入该工艺大规模生产的早期开发阶段。

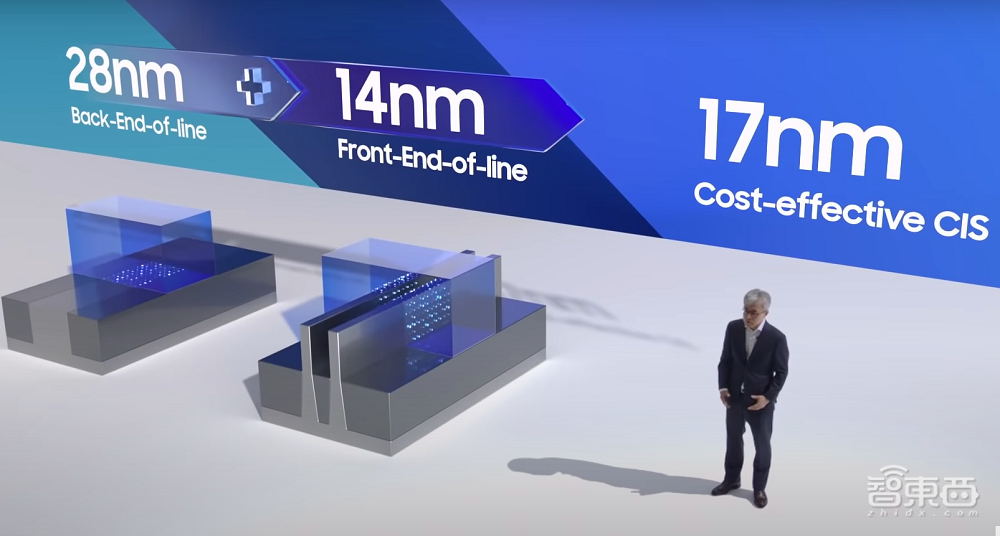

除了3nm和2nm等先进制程,三星电子还首次推出了17nm FinFET专业工艺技术,该工艺适用于CIS(接触式图像传感器)、DDI(显示驱动IC)、MCU(微控制器)等领域。

17nm FinFET专业工艺技术结合了28nm的后端工艺和14nm的前端工艺,Siyoung Choi认为,这一工艺能够为客户带来显著的成本优势,帮助客户完成从28nm到14nm的过渡。

▲三星电子17nm专业工艺特性

▲三星电子17nm专业工艺特性

与28nm相比,三星电子的17nm FinFET专业工艺技术面积减少了43%,性能提高了39%,功率效率提高了49%。

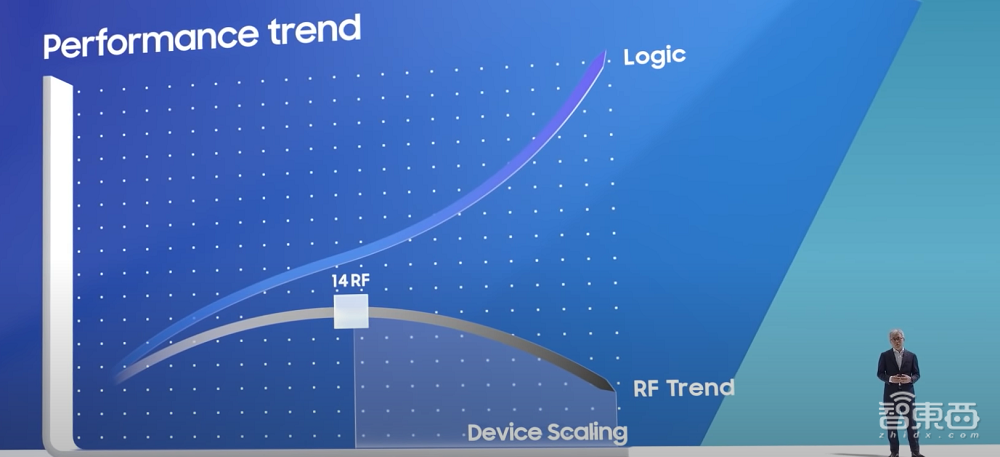

在5G技术的推动下,射频(RF)技术正成为行业的关键,但是射频技术并不适应设备的几何缩放。通过异构集成等创新技术,三星电子的8nm射频平台将改变发展曲线,提升市场竞争力。除此之外,三星电子还正在推进基于14nm工艺的3.3V磁性随机存取存储器(eMRAM),从而提升写入速度和密度。

▲逻辑芯片和射频芯片性能趋势

▲逻辑芯片和射频芯片性能趋势

二、平泽将成GAA芯片生产基地,美国新晶圆厂地址考虑中

在晶圆代工方面,Siyoung Choi提到三星电子是第一个将EUV(极紫外)技术引入大规模生产的厂商,三星电子在这一领域的经验将使其能够减少扩充产能所需的时间。

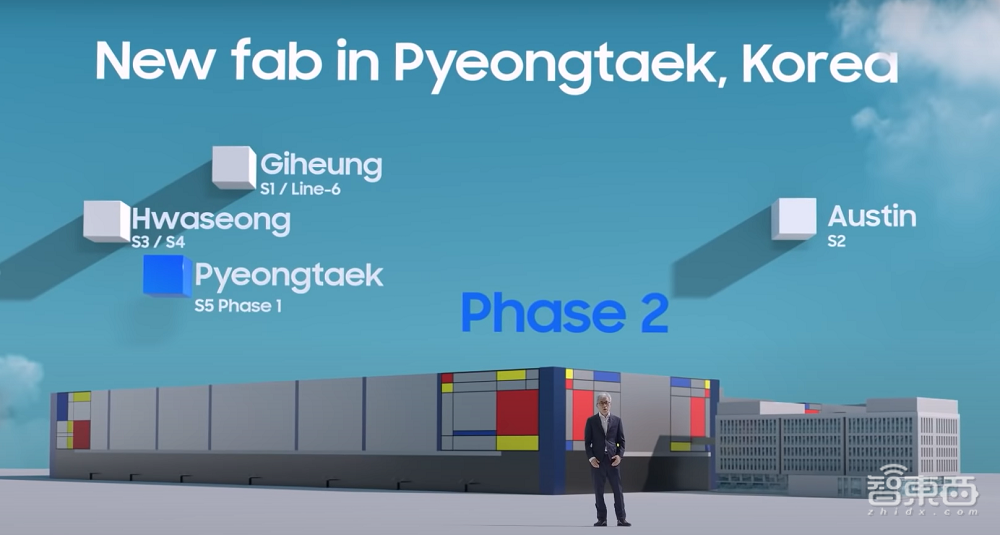

当前,三星电子在全球共有4个晶圆制造基地。在韩国,三个晶圆厂位置较近,可以共享基础设施。其中三星计划在平泽扩充产能,生产基于GAA结构的产品。

▲三星电子代工厂分布

▲三星电子代工厂分布

在美国,三星除了在得克萨斯州奥斯汀外,还计划建设新的晶圆厂。但Siyoung Choi并没有透露更多的信息,仅告知有几处地点正在考虑中,具体信息将在之后宣布。

他谈道,三星电子的代工业务重点是高性能计算(HPC)和人工智能(AI)、物联网、汽车3个平台。三星电子能够为每一个产品提供全面的解决方案,帮助客户更快完成发布。

具体来说,在高性能计算和人工智能领域,三星电子能够提供Large die设计方法、2.5D和3D先进封装技术、高性能IP等;在移动和物联网领域,三星电子能够提供低功耗设计方法、安全互连IP和嵌入式MRAM产品;在汽车领域,其产品符合ISO 26262和AEC-Q100安全认证。

最后他分享称,三星正在和IBM这样的公司在人工智能、高性能计算等领域进行合作,覆盖工艺开发到高性能芯片等各个方面。

三、2nm开战:IBM率先发布,台积电2024年量产

当下,三星、英特尔、台积电等厂商都已瞄准了3nm以下的先进制程。

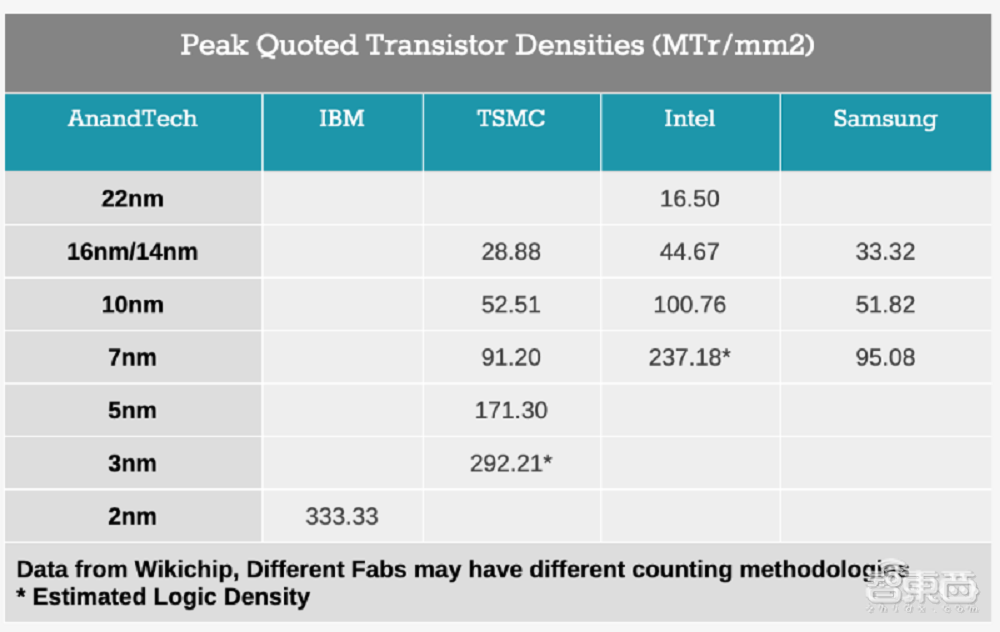

据路透社报道,三星、IBM和英特尔已签署联合开发协议,共同研发2nm制程工艺。今年5月,IBM率先发布全球首个2nm制程工艺,预计能够在“指甲盖大小的芯片上”集成约500亿个晶体管,但该工艺距离量产仍有距离。

外媒报道称,IBM的2nm工艺或能实现在芯片上每平方毫米集成3.33亿个晶体管,远超此前三星5nm工艺的每平方毫米约1.27亿晶体管数量,极大地提升了芯片性能。

▲IBM、台积电、英特尔、三星各制程节点晶体管密度对比(来源:AnandTech)

▲IBM、台积电、英特尔、三星各制程节点晶体管密度对比(来源:AnandTech)

面对三星、英特尔和IBM的联合开发,晶圆代工龙头台积电也加大了对先进制程的研发投入。据媒体报道,台积电预计将在2024年实现2nm工艺的量产,全面量产则可能要到2025年-2026年。

除了上述芯片厂商,欧盟也提出了2nm芯片战略。今年3月,欧盟提出最新的数字化转型目标,要求在2030年实现2nm逻辑芯片的生产。9月份,欧盟又推动设立新的《欧洲芯片法》,意图打造最先进的欧洲芯片生态系统。

结语:2/3nm研发竞赛或影响代工市场走向

因为缺芯加剧,晶圆代工领域受到了极大关注。台积电、英特尔、三星电子等都加大了对先进制程研发和晶圆产能扩张的投入。

随着芯片尺寸逼近物理极限,芯片制程推进十分困难,“摩尔定律失效”不断被行业提起。尽管如此,台积电、英特尔、三星等巨头不会放弃对3/2nm甚至1nm的先进制程研发,这场竞赛更将影响未来代工市场的走向。