芯东西(公众号:aichip001)

作者 | 高歌

编辑 | Panken

芯东西12月14日报道,今天,英特尔制造、供应链和营运集团副总裁兼战略规划部联席总经理卢东晖向芯东西等媒体详细解读了英特尔在今年IEEE国际电子器件会议(IEDM)上发布的8篇论文。

这是英特尔首次在这一学术会议上发布如此数量的论文,据卢东晖分享,本次英特尔发布的很多新研究特点是基于当前的芯片制造工艺,之后有应用于现有的产线的可能,对英特尔IDM 2.0战略有着重要意义。

本次在IEDM会议上发表论文的是英特尔组件研究部门,这是英特尔专注于前沿研发的部门,被称作“英特尔技术研发部门中的研究团队”,其发表的论文主要集中在晶体管微缩技术、在功率器件和内存方面基于新材料的研究和量子计算器件3个领域。

▲英特尔在IEDM 2021上的研究突破

▲英特尔在IEDM 2021上的研究突破

一、新互连技术提升10倍密度,3D CMOS堆叠降低50%芯片面积

对于先进制程的演进,卢东晖将其比作爬山,人们知道山顶在哪里,但是不清楚路在哪里,也不确定自己到底能否登顶、会花费多少时间,这都是行业领先者需要考虑的问题。

摩尔定律成为了推动行业不断投入研发的重要原因,而且这一定律对产业界合作也起到了关键作用。此前,芯片制造、材料、设备厂商产品迭代时间并不一致,产品迭代较为混乱,整个产业链合作效率较低。

摩尔定律则在一定程度上成为了芯片产业链的路线图,上下游厂商可以在相近的时间节点进行产品迭代,使行业合作效率更高。

同时,更高的组件密度能够让芯片实现更高的吞吐量、增加新的特性和功能、降低成本、提高能效等。卢东晖以3D NAND闪存为例强调了芯片制程代差对于企业的重要,他提到领先两代的产品以30%的良率进行生产,其成本就要低于90%良率生产的落后产品,更高的制程代差甚至出现“在月球造都要更便宜”的现象。

具体到本次发布的论文,英特尔在晶体管微缩领域的研究突破主要为封装中互连密度的提升、3D堆叠的CMOS晶体管结构和新的2D材料。

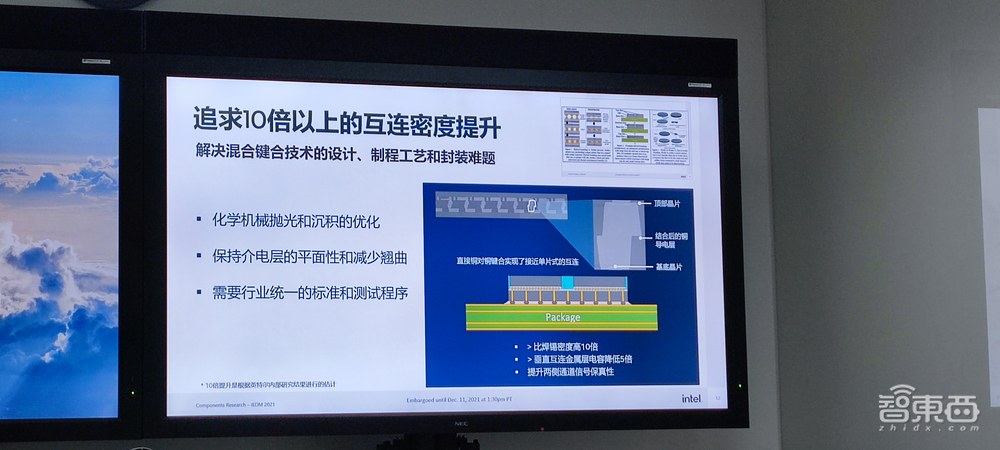

在封装互连密度的研究中,英特尔研究团队实现了铜对铜的近单片式互连。新的互连方式比焊锡密度高10倍,使垂直互连金属层电容低5倍。

不过这对表面平整度要求更高,需要厂商对化学机械抛光和沉积工序进行优化,保持介电层的平面行和减少翘曲,并要有行业统一的标准和测试程序作为支撑。

▲新互连技术展示

▲新互连技术展示

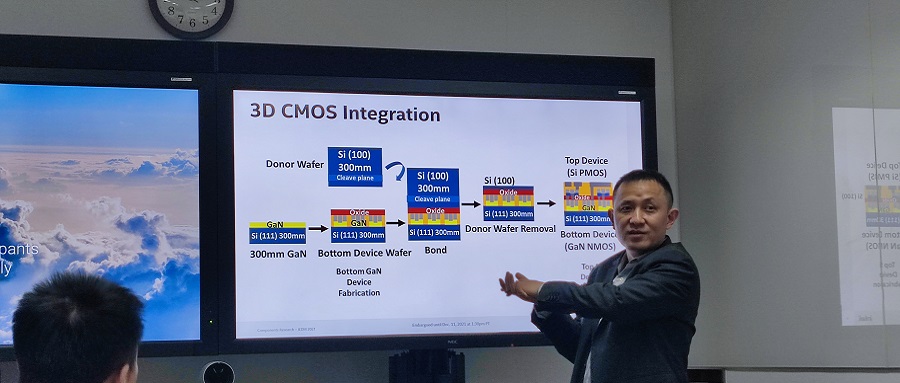

在晶体管结构上,英特尔实现了3D CMOS的堆叠,通过将源极和漏极直接堆叠的方式,降低了30%-50%的芯片面积。

卢东晖称,这有两种不同的实现方式,一种是依序,即上下层晶圆依序堆叠加工;另一种则是自对准,即上下层晶圆对准后同时进行架构,能够将栅极间距缩减至55nm。

在卢东晖个人看来,3D CMOS堆叠结构可能会在GAA(全环绕栅极)之后被用于先进制程芯片生产。

▲3D CMOS堆叠技术展示

▲3D CMOS堆叠技术展示

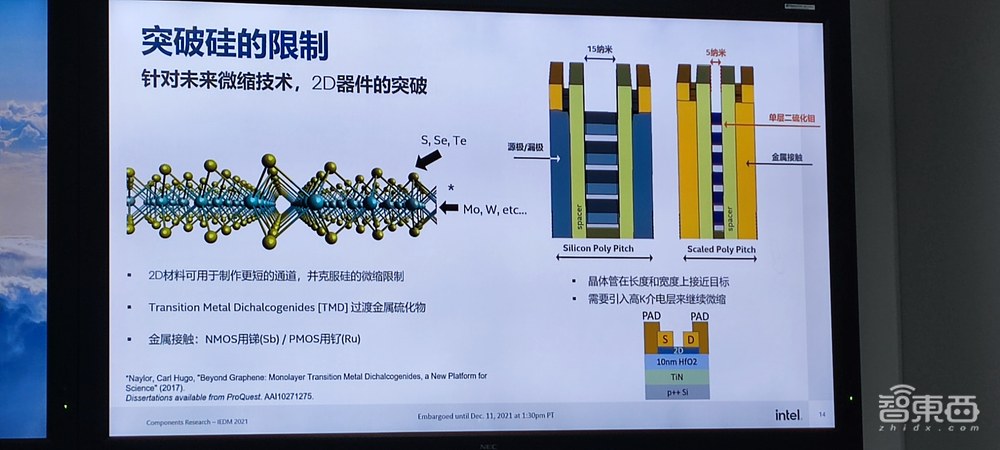

在新材料方面,英特尔发现了一种TMD(过渡金属硫化物),这是一种2D材料,其单层结构仅有数个原子厚度,能够克服硅半导体在缩减到一定规模后出现的量子隧穿问题。

在论文中,英特尔使用锑(Sb)和钌(Ru)两种金属作为NMOS两级,使其间距从15nm缩减至5nm。卢东晖称,这种新材料可用于硅基材上,构建新的芯片结构,实现高性能异构。

▲2D新材料展示

▲2D新材料展示

二、在300mm晶圆上集成氮化镓器件,铁电存储实现2纳秒读写速度

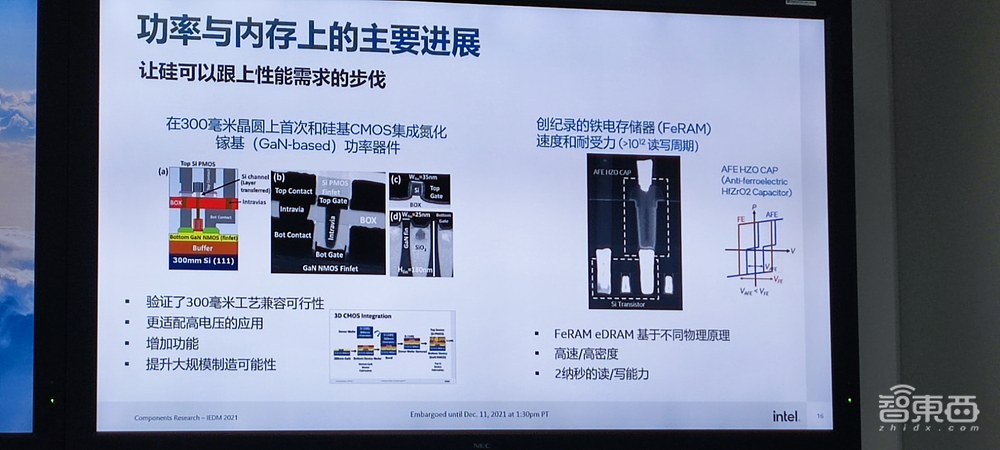

在功率器件方面,英特尔首次在300mm(12英寸)硅晶圆上和硅基CMOS集成了氮化镓(GaN)功率器件。

卢东晖称,该研究验证了氮化镓器件和300mm工艺兼容的可行性,提升了氮化镓器件在现有晶圆厂机台上进行大规模生产的可能。

当前氮化镓器件往往基于8英寸以下的晶圆制造,其成本较高。而这项研究将对第三代半导体的大规模制造起到重要的作用,扩大其应用范围与规模。

此外,英特尔还实现了一众铁电存储器(FeRAM),具有2纳秒的读/写能力。

▲英特尔功率器件和内存上的研究进展

▲英特尔功率器件和内存上的研究进展

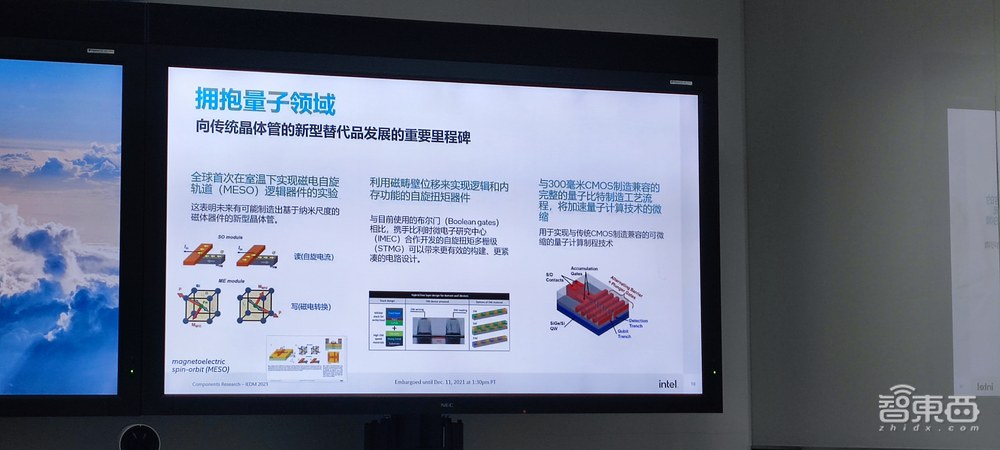

三、实现首次室温量子逻辑器件实验,用硅工艺造量子比特

在量子领域,英特尔的研究也有所突破。

当前量子计算有超导、光电、硅基芯片等不同的实现路径,由于超导方式对量子比特的操控性较好、可扩展性较强,谷歌、中科院团队等都采用了这一方案。但是由于超导需要超低温(达到或接近绝对零度)的环境,使其应用具有一定难度。

英特尔则采用了硅基芯片的方式来实现量子计算。本次IEDM会议上,英特尔展示了全球首次在室温环境下实现了磁电自旋轨道(MESO)逻辑器件的实验。

在纳米尺度下,英特尔研究团队通过磁体的自旋电流实现芯片读入功能,通过电磁转换实现写入功能,展现了基于纳米尺度的磁体器件晶体管可能性。

此外,英特尔和比利时微电子研究中心(IMEC)在自旋电子材料研究方面取得了进展,双方合作研发了自旋扭矩多栅极(STMG)结构,可以通过磁畴壁位移实现逻辑和内存功能。

最后,英特尔还展示了完整的300mm量子比特制程工艺流程。值得注意的是,该量子计算工艺与当前的300mm CMOS制造工艺兼容,扩展了量子计算芯片大规模制造的可能。

▲英特尔量子领域研究进展

▲英特尔量子领域研究进展

结语:英特尔三大领域研究进展宣告竞争决心

在今年的IEDM会议上,英特尔为我们展示了其在制造工艺上的前沿技术,相比很多基础研究,这些技术更注重在实际工艺产线中的生产,体现了英特尔的研发实力。

自英特尔CEO帕特·基辛格提出IDM 2.0战略以来,英特尔也高调宣布将重拾芯片制造领导地位,本次的各项新研究则揭露了英特尔高调宣传背后的技术研发实力。未来晶圆制程竞争恐更加激烈。