12月23日,智东西公开课联合新思科技推出「新思科技DesignWare IP公开课」,共有两场,聚焦新思科技DesignWare IP如何帮助开发者加速芯片设计与集成。第一场「计算存储SoC专场」已于12月28日完成了直播讲解,由新思科技解决方案部高级技术经理王伟主讲,主题为《使用支持AI的控制器SoC构建计算存储系统》。

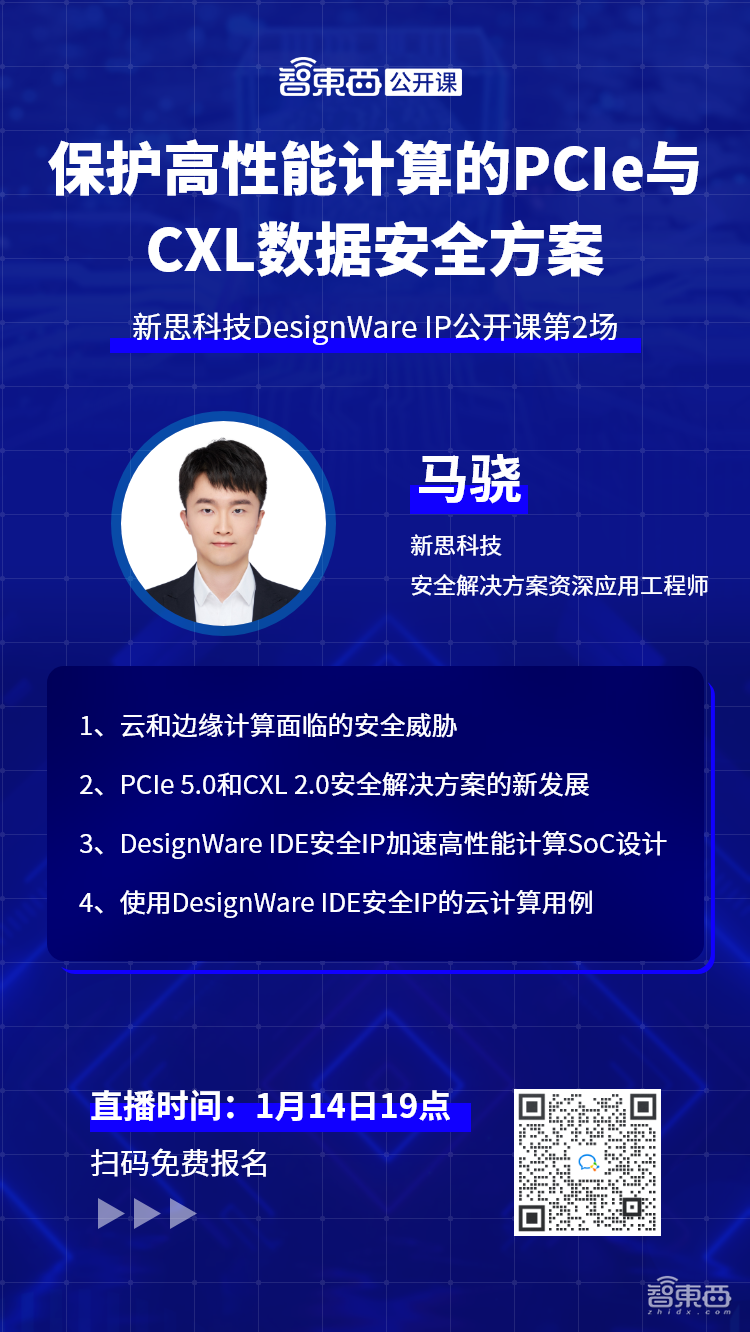

1月14日,「新思科技DesignWare IP公开课」第二场将开讲,定名为「PCIe 5.0和CXL 2.0数据安全专场」,由新思科技安全解决方案资深应用工程师马骁主讲,主题为《保护高性能计算的PCIe与CXL数据安全方案》。

随着人工智能、大数据、云计算技术的不断成熟落地,极大的推动了互联网数据的增长,云计算正在经历重大变革。为了应对数据增长带来的数据传输和存储压力,数据中心接口和存储技术需要不断创新,以具备更大容量和更强的性能,满足不断发展的数据中心高性能计算架构需求。诸如PCIe 5.0和CXL 2.0之类的高速接口得到了快速发展,并在云计算系统、存储系统中得到了广泛的应用。

不过,当大量的数据通过PCIe 5.0和CXL 2.0等高速接口,在计算单元和存储单元转移的过程中,也面临着被恶意破坏、替换、修改或窃取的风险。为了保证数据安全,PCI-SIG和CXL标准组织在2020年末将完整性和数据加密等安全要求添加到 PCIe 5.0和CXL 2.0规范中。

2021年2月,新思科技推出DesignWare IDE安全模块,能够协助使用PCIe 5.0架构或CXL 2.0接口进行高性能计算(HPC)SoC设计的开发者,有效防范数据篡改和物理攻击的风险。DesignWare IDE安全模块通过基于AES-GCM算法的高效加解密和身份验证方式来保护敏感数据,同时满足PCIe 5.0和CXL 2.0 IP核的性能、延迟要求和最新的接口标准,并使用新思科技的DesignWare控制器IP核进行设计和验证,能够帮助开发者加速高性能计算SoC的开发与集成。

在本次讲解中,马骁老师将从云和边缘计算面临的安全威胁、基于PCIe 5.0和CXL 2.0安全解决方案的最新进展、使用DesignWare IDE安全IP加速高性能计算SoC设计及云计算用例等方面进行系统讲解。

本次专场将在智东西公开课直播间以视频直播形式进行,包含主讲和问答两个环节。主讲环节40分钟,问答环节20分钟。每个环节主讲老师都将通过视频直播进行实时讲解与互动。

专场内容

主题:保护高性能计算的PCIe与CXL数据安全方案

提纲:

1、云和边缘计算面临的安全威胁

2、PCIe 5.0和CXL 2.0安全解决方案的新发展

3、DesignWare IDE安全IP加速高性能计算SoC设计

4、使用DesignWare IDE安全IP的云计算用例

讲师介绍

马骁,新思科技安全解决方案资深应用工程师,负责Security IP(包括TRNG, Crypto Accelerators, HDCP, tRoot等)的售前支持和咨询工作。在加入新思科技之前,他曾在Elliptic Technologies工作, 并拥有多年的IP设计和支持经验。马骁毕业于清华大学,拥有微电子学专业本科及硕士学位。

专场信息

直播时间:1月14日19:00

直播地点:智东西公开课直播间