芯东西(公众号:aichip001)

作者 | ZeR0

编辑 | 漠影

芯东西8月18日报道,今日,2022世界半导体大会暨南京国际半导体博览会在南京开幕,中科院院士、深圳大学校长毛军发在开幕式暨高端论坛上发表主题演讲。

在简要回顾集成电路的定义、发展简史及我国落后原因后,毛军发院士着重分享了集成系统的发展趋势和挑战,以及应重点关注的4个关键科技问题。

毛军发院士认为:“过去60年是集成电路的时代,未来60年是集成系统的时代。”他提到随着摩尔定律面临极限挑战、转折点临近,半导体技术将从电路集成走向系统集成的发展新路径,这为我国变道超车发展提供了历史机遇。

一、EDA、装备、器件与电路落后成因

集成电路(IC)是将晶体管、电阻、电容和电感等元器件及互连线制作(集成)在一小块半导体晶片或介质基片上,形成具有预期功能的电路。

所有元器件在结构上组成一个整体,使电路向着高密度、大规模、小型化、低功耗、低成本和高可靠性方向发展。

集成电路是一个国家综合科技实力乃至综合国力的反映,是“有钱也买不到”的被“卡脖子”的关键高科技赛道,中国每年都花费巨资进口集成电路,高端芯片基本依赖进口。

回溯我国集成电路落后的原因,既有先进技术受西方封锁,也有此前曾有一段发展阶段瞻前顾后,产学研脱节。

具体到细分领域,EDA落后的主要原因是研发算法的较多,但很零散,没有规划、集成;大型软件工程能力较弱,经验较少,用户不愿意用国产软件工具,恶性循环。

半导体装备落后则主要是受整体能力和市场环境等多方面因素影响。器件与电路落后的原因包括材料落后,工艺的精细度、稳定性不足,缺工匠精神和工艺大师。

现阶段,我国集成电路急需大批的高端人才。

二、“未来60年是集成系统的时代”

当前集成电路行业的发展方向包括延续摩尔定律(More Moore)和绕道摩尔定律(More than Moore),前者面临物理原理极限、技术手段极限、经济成本极限等挑战,后者的主流趋势有chiplet、异质异构、集成系统等。

毛军发院士判断,过去60年是集成电路(IC)的时代,而未来60年是集成系统(IS)的时代。

他谈道,集成电路(芯片)只是手段,微电子系统才是目的。集成系统从系统角度进行一体化设计制作,将各种芯片、传感器、元器件、天线、互连线等制作集成在一个基板上,形成具有预期功能的系统,所有芯片和元器件在结构上组成一个整体,使系统高密度、小型化、强功能、低功耗、低成本、高可靠、易设计、易制作。

这种思路,可以进一步提高系统的设计效率和综合性能,减少系统的成本,增加其可靠性,并降低对芯片设计以及设备的要求。

实现从集成电路到集成系统的跨越有三点意义,是复杂微系统集成技术发展的新途径、后摩尔时代集成电路发展的新方向,也是半导体技术变道超车的发展新机遇。

小芯片或晶粒(chiplet)技术就是一种特殊的集成系统概念,它将单一先进工艺的大芯片分解成多个特征模块,每个模块(小芯片)用各自最适合的工艺实现。小芯片技术与SoC逆向思维:SoC将半导体IP平面集成在一个芯片里,SoIC则是将多个chiplet以3D堆叠集成。

当前集成电路前道设计加工与后道封装逐步收敛融合。封装集成技术的重心正慢慢从传统后端封装移到前端半导体代工。

中国台湾晶圆代工龙头企业台积电的3DFabric平台的SoIC采用最先进封装互连技术Hybrid Bonding,堆叠芯片间互连间距可以小到亚微米。目前台积电已实现用3DFabric完成12层堆叠SoIC。

如果台积电助推的3DFabric,特别是SoIC,成为下一代芯片系统的主流技术,那么台积电将在半导体行业更加强势,而中国大陆原本代工较弱、封装较强的局面将变成代工和封装都落后。

另一个集成系统的例子是封装中天线(AiP)技术。AiP是指包含无线芯片的封装结构中(上)实现的天线,相比于普通分立天线,AIP具有更好的系统性能、更小的PCB面积、更低的成本,以及更短的研发周期。

第三个例子是多功能无源元件技术。电子系统中包含大量的无源元件,不同功能元件、天线级联需大量转接,引入了额外的损耗与体积;将多种元件结合为协同设计的多功能元件,则能显著减少系统所需元件和转接个数,降低插损,实现小型化。

三、集成系统面临4个关键科技问题

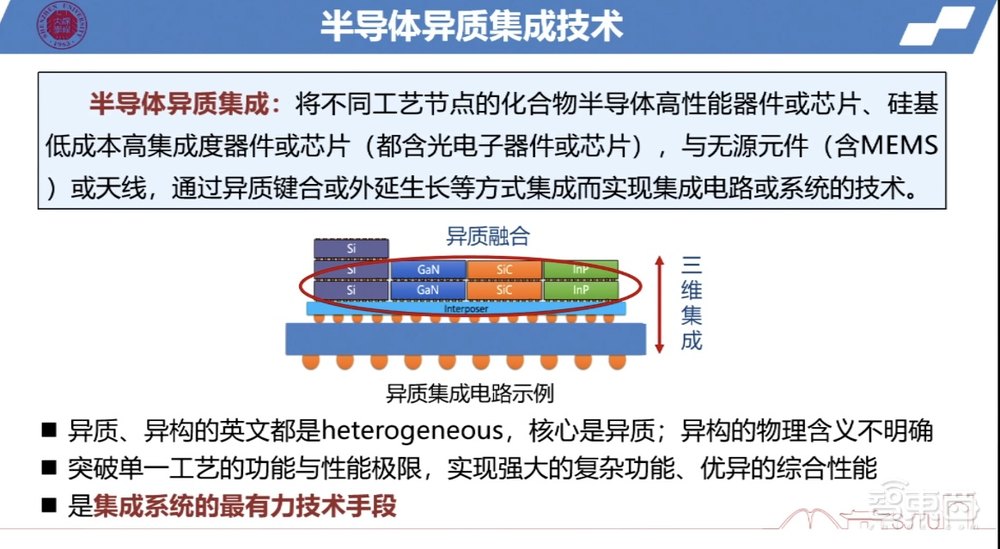

半导体异质集成技术是集成系统的最有力技术手段,能突破单一工艺的功能与性能极限,实现更强的复杂性能、优异的综合性能。

它将不同工艺节点的化合物半导体高性能器件或芯片、硅基低成本高集成度器件或芯片,与无源元件或天线,通过异质键合或外延生长等方式集成而实现集成电路或系统的技术。

在毛军发院士看来,集成系统正面临4个关键科技问题。

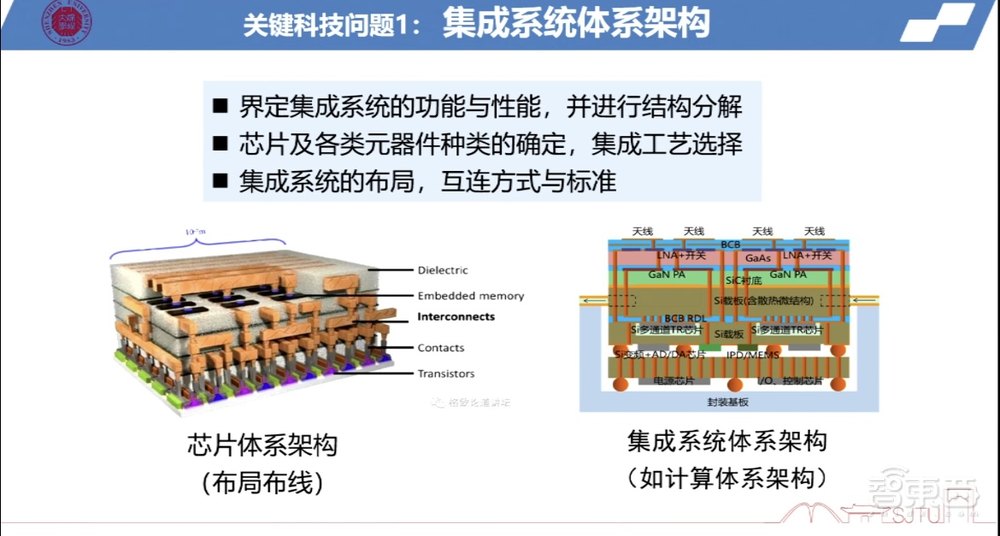

首先是集成系统体系架构,包括界定集成系统的功能与性能,并进行结构分解;芯片及各类元器件种类的确定,集成工艺选择;集成系统的布局,互连方式与标准。

第二是自动化智能化协同设计,既包括电磁-热-应力多物理协同设计,有源/无源电路/天线及数字、模拟、射频电路的多功能协同设计,也包括IP、IPD、PDK、chiplet等复用。

第三是异质界面生成与工艺量化调控机理。集成系统工艺参数调整受制于电、热、应力等多物理场特性。因晶格、膨胀系数差异,需建立异质界面动力学,认识扩散、成核、粘合机理,通过界面调控融合,实现高可靠异质集成。

第四是无源元件、天线小型化,这对整个射频集成系统至关重要。无源元件最多可占射频电子系统元件总数的90%,系统总面积的80%,面积、工艺与芯片差异大。由于射频损耗、电磁兼容与热问题,给小型化与性能提高带来挑战,需突破传统思路,提出新的工作机理和设计理论。

结语:国内外均在加紧集成系统相关技术攻关

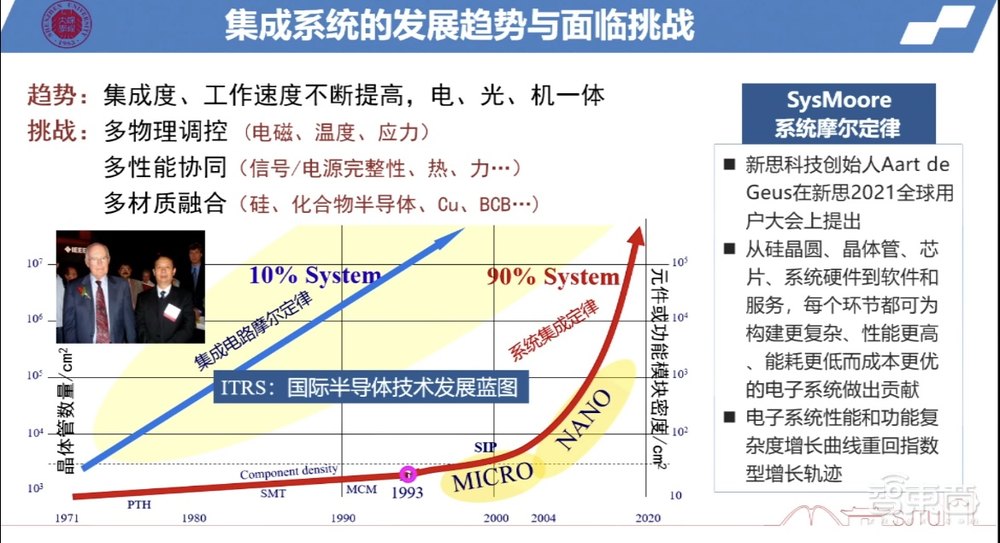

毛军发院士分享说,目前集成系统的集成度、工作速度正不断提高,同时面临多物理调控、多性能协同、多材质融合这三个主要挑战。

国内外在政策与产业方面均将集成系统相关技术视作重要发展方向。美国在2018年启动的联合大学微电子计划和电子复兴计划,重点均包括异质集成。国内上海交通大学、中电集团、中科院、长电科技等产学研机构也在开展系统封装研究。此外日本、韩国、新加坡等地均有异质集成相关研究的计划。台积电、英特尔、IBM、三星等国内外半导体大厂均在做3D封装集成研究。