芯东西(公众号:aichip001)

编辑 | GTIC

芯东西9月14日报道,在刚刚落幕的GTIC 2022全球AI芯片峰会期间,知存科技创始人兼CEO王绍迪进行了以《WTM存内计算芯片应用及发展》为题的演讲。

王绍迪说,与传统冯·诺依曼架构相比,存算一体具备明显的能效、成本优势。但未来要满足更多场景需求,存算一体在通用性、工具链、精度上的优势还有待补齐。他预测未来3-5年内,存算一体可能实现每年超过8倍的算力提升。

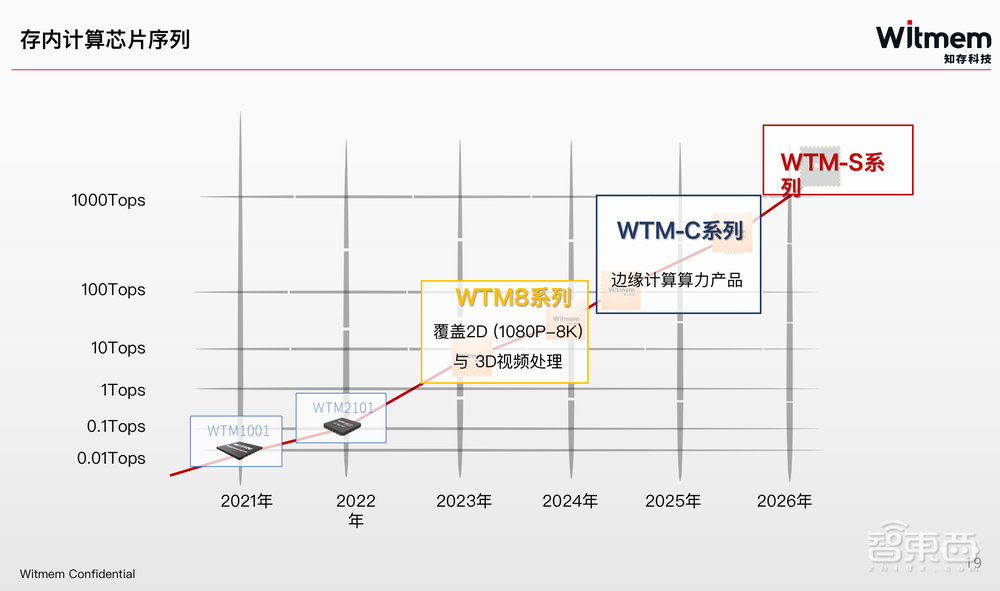

知存科技的存算一体芯片已进入多个可穿戴设备产品,年销量预计达百万。此外,王绍迪首次公开知存科技未来五年的产品路线图,预计明年发布覆盖2D与3D视频处理场景的更高算力WTM8系列,在2025年前发布边缘计算产品WTM-C系列。

以下为王绍迪的演讲实录:

这应该是我第三次参加AI芯片峰会。这一次非常高兴的是存算一体AI芯片有了专门的论坛。

我是知存科技的创始人兼CEO王绍迪,我们公司专注于存内计算芯片的研发、生产和销售。今天的介绍会有4个部分:第一部分关于知存科技以及存内计算芯片的简介;第二部分讲一讲存内计算的优势;第三部分介绍存算一体WTM2101芯片以及它目前的应用场景和优势;第四部分介绍知存科技的产品还有未来规划。

一、技术原理基于欧姆定律,矩阵乘法效率倍增,发展潜力巨大

知存科技2017年成立,到现在快接近5年时间。

成立之前,我们首席科学家郭昕婕从2012年开始做存内计算芯片的研发,2016年已经完成国际上首个Flash存算一体芯片的验证,算是一个从0到1存算一体芯片的验证,这也是第一个可以做多层深度学习网络的存算一体芯片。

有了这样的成果,在2017年,我跟郭昕婕创立了知存科技,专注于存算一体芯片的研发。我们成功量产了一款名为WTM2101的存算一体芯片。

WTM2101芯片目前已经量产商用,用在多个产品中,后面我再作介绍。

存算一体和传统计算的区别是使用存储器单元做计算。主要用存算一体技术去解决矩阵乘法的计算,人工智能99%都是矩阵乘法,存算一体非常适合人工智能或者深度学习的计算,可以把存算一体应用到人工智能芯片中。

存算一体最基本的技术原理,如果做模拟的存算一体,是利用欧姆定律的乘法。我们知道欧姆定律是电压×电导=电流,这是物理上的计算原理。如果我们能够利用存储器实现物理的计算原理,一个存储阵列就可以实现百万级甚至千万级并行的计算,计算并行度要高出很多。

常用的向量矩阵乘法在深度学习计算中,如果转化到存算一体中,只需要1次存储器的读取操作,就可以完成百万级参数的乘法和加法计算。如果用传统的GPU架构,百万级的乘法加法计算,光是存储器的读取次数就要超过5万次。这是1次存储器的操作和5万次存储器操作的区别。

在存储器操作有巨大区别的情况下,存算一体计算的能效、速度、算力、成本就有很大的优势。基于这样的优势,知存科技专注开发存算一体芯片。

存算一体芯片目前已经实现商用,而且未来还有很多的迭代优化空间,包括存算一体计算的速度加快、计算的精度提高、面积持续减少、规模持续加大。

我认为未来几年都是存算一体飞速发展的黄金时代,这就像以前90年代摩尔定律一样,每年都有几倍的算力提升。我认为存算一体在未来3-5年内可能提升速度更快,每年可能都超过8倍的算力提升。

二、减少数据搬运代价,成本、能效优势明显

存算一体的优势目前主要是在成本、算力、功耗上,它在通用性、工具链和精度上的不足还需补齐。

为什么存算一体它从成本、算力、功耗上会有这样的优势?

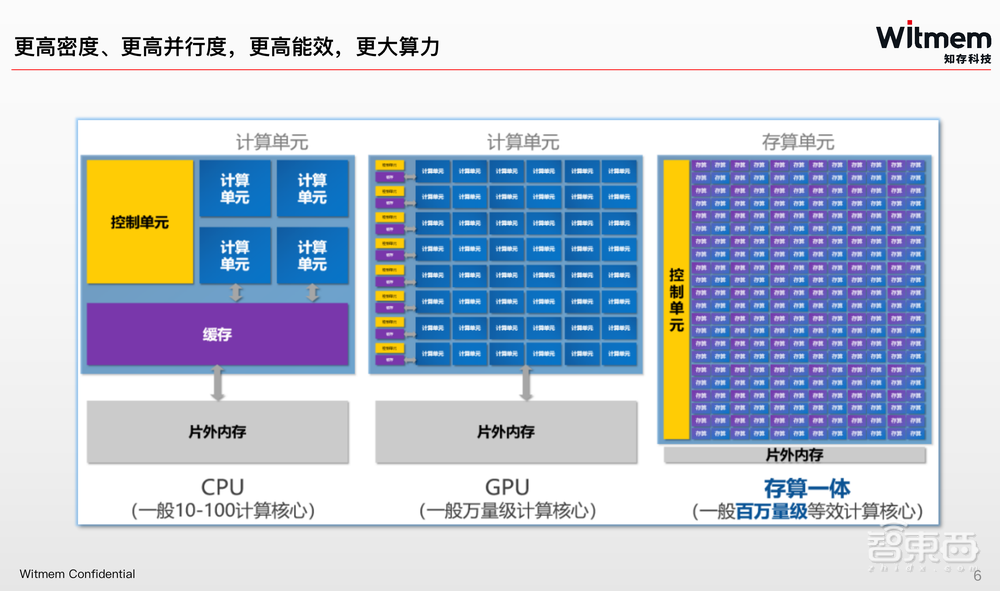

我们可以看CPU、GPU和存算一体的计算架构,CPU的计算架构相当于计算单元有很多,有多级的缓存。GPU也是类似,但它计算的单元数量会更多,计算的并行度会更多。

存算一体跟前面的架构相当不同,存算一体相当于没有统一的缓存存储,可以理解成计算和存储是一体化且是分布式。

如果从架构方面来看比较复杂,我们可以拿核酸检测举例,可以想象CPU是1个人给1栋楼的居民一点点地做核酸检测,GPU相当于1000个人给1000个居民楼做核酸检测,但冯·诺依曼架构就是检测人必须呆在一个大的园区中,1000个人都在一个广场上,1000个楼的居民去做检测。

未来计算的数据量会越来越大,现在可能是GB、TB级,未来可能是PB级,计算并行度也从现在的百万级,到千万级、亿级。相当于我们现在要做核酸检测,可能从原先一个小区的人变成我们需要把一个城市的人,1万倍核酸检测的工作人员聚集一起,整个城市的人过去做核酸检测,这样可想而知大家都会堵在路上。

这就变成数据搬运的代价是非常大的,因为人从家里到核酸检测的园区,可能需要走一天的时间去做核酸检测再回来,这就跟现在冯·诺依曼的计算瓶颈是一样的,数据搬运占用了可能95%以上的功耗,占用了80%以上的时间。

随着算力越来越大,它的问题会越来越严重,存算一体是一种可以缓解这种问题的技术,我们不再需要有统一的人一点点做核酸检测,它的效率就有很大的提升。

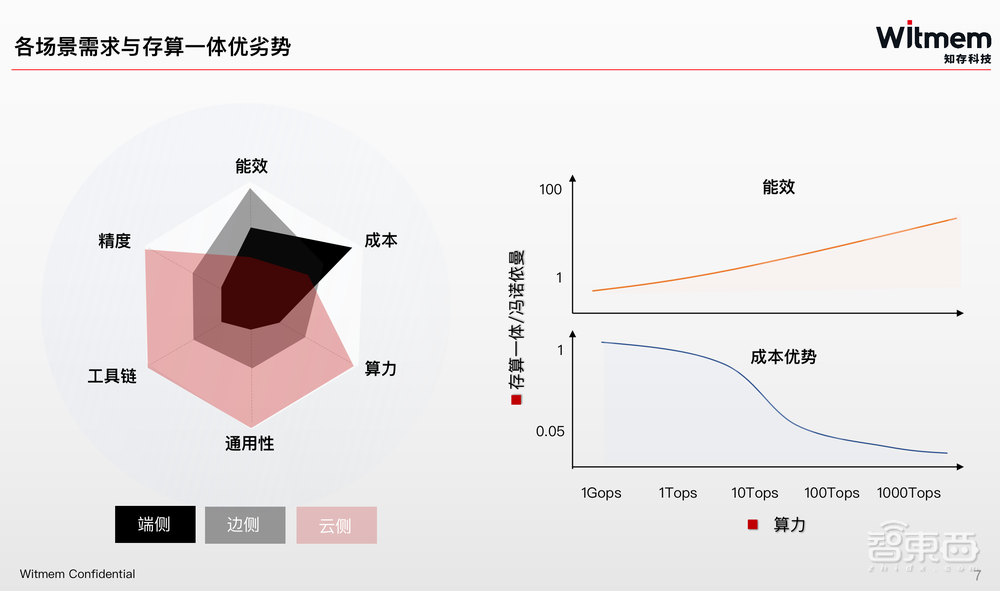

所以这里面,我们也在分析端侧、边侧和云侧存算一体到底应用优势在什么。

左边总结了一个对端侧、边侧、云侧的计算需求的优势。端侧最重要的是成本;边侧相当来说能效比较重要,因为端侧很多场景下受散热限制或者体积限制,但它对成本、精度、工具链、算力都有一定的要求;云侧相对来说能效也一样重要,但成本相对不是那么重要,它对算力、通信、工具链、精度都有不同方面的需求。

存算一体在算力、成本、能效都有一定的优势,但在不同的应用场景下它的优势也是有所侧重,随着算力在增大的情况下能效会逐渐提高。

这点可以很容易理解,不仅存算一体,像现在的NPU还有AI芯片,都是算力越大的时候,能效在往前提升。但传统的NPU还有AI芯片,它有一定的瓶颈,达到一定算力的程度下,再往上的能效就很难提升了,这主要受到存储墙的限制。

但存算一体的能效随着算力在增大,它能够提升的空间是更大的。另外是成本,算力更大,存算一体成本下降也是快的,因为算力越大的时候,存算一体的计算单元它的存储器所占的面积、所占的成本以及可拓展性的优势就发挥出来了。

算力很小的情况下,存储器只占芯片中非常小的一部分,算力很大的时候甚至可以用专用的工艺去把存储器的密度提高,把存储器的工艺做的成本更低,它的集成度也做得更高。

我们认为像存算一体,预计它的每Tops的成本可以做到普通AI芯片或者GPU的大概1/20,这是它一个很大的优势。另外存储器使用工艺的成本也比大算力下先进工艺要低很多,所以存算一体的大算力成本也有很大的优势。

三、量产不到半年,落地多款可穿戴设备

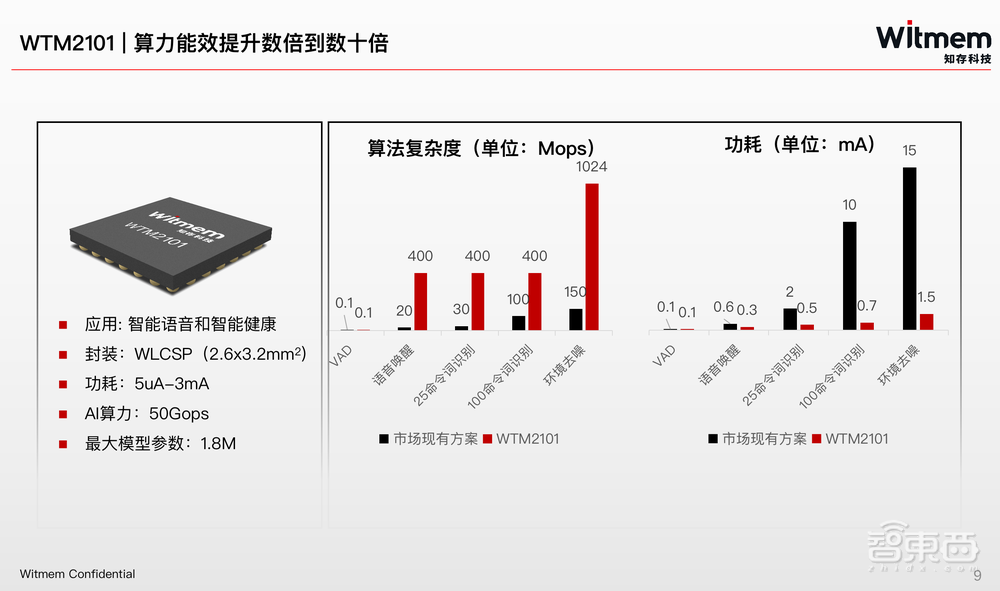

我们公司去年发布、今年量产了一个WTM2101芯片。这个芯片的特点,常规使用下功耗是在5uA-3mA的量级,AI算力可以达到50Gops,可以存1.8兆个算法参数,用存储单元做深度学习计算,一般可以运行1-3个算法,因为一般算法大小在端侧下大概几百K级别,有的可能到1M的级别。

WTM2101和现有市场上做得很好的芯片方案相比,围绕典型应用场景在算力、功耗上都有很大的优势,两个乘起来大概有个几十倍的优势。所以它在能效上或者在算力上、功耗上都有不同幅度的提升。

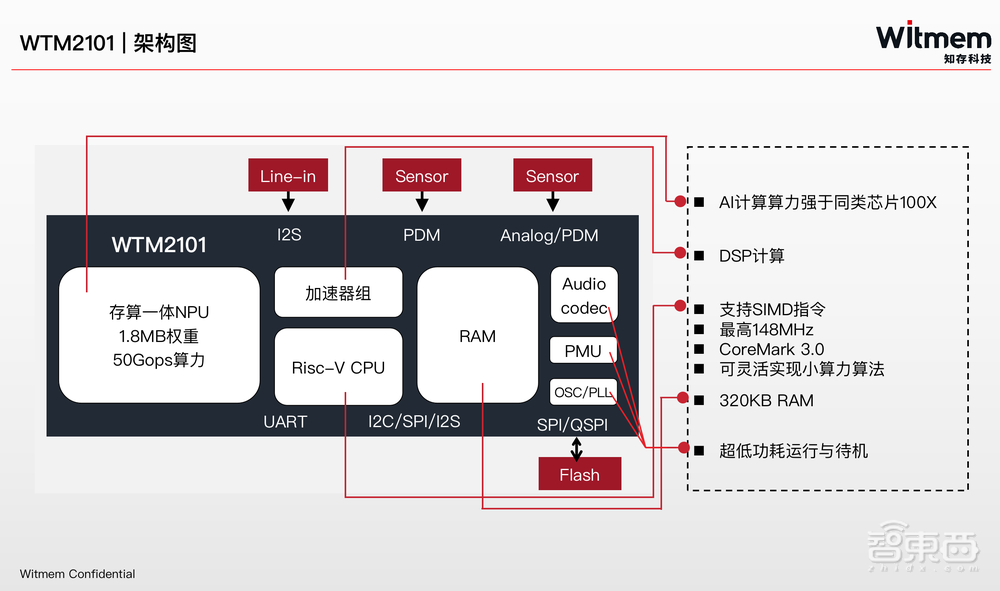

这是WTM2101芯片的架构。它不是一个专用芯片,而是通用、可开发的,这里面有1.8M的存算一体,我们也叫它NPU,做人工智能计算。此外有个CPU,还有加速器,加速器是标准的ASIC,做一些存内计算做不了的非AI计算,它的可开发性也是比较强的。另外有个320KB RAM可以实现非AI的算法,配合148MHz的CPU,在常规非AI的算法都可以跑得游刃有余。

我们的接口做了很多低功耗的接口设计,可以连多个传感器去实现传感器的取出和实时处理,同时也支持音频信号的直接输入和直接处理。

这个芯片主要用在可穿戴场景中,因为可穿戴对功耗一般在几毫安的限制,像WTM2101一般功耗是在1mA以内,所以在这个场景下它增加的功耗很小,但提升算力很大,一般会把现有产品的人工智能算力提高几百倍以上,包括像耳机、手表,功能像语言识别、语音增强、健康监测、环境识别、远场唤醒、运动识别、视觉识别、事件检测,这是芯片的常用场景。

我简单介绍一些目前在客户应用中用起来比较好的功能。

第一个是AI降噪算法。用芯片可以跑比较大的模型,跑1Gops的算力,这个算力主要做的算法采集外界的声音,包括人声和噪声,基于深度学习的计算,可以把人声和噪声分离开,生成一个干净的人声。

这纯靠算法层面去做噪声人声分离,所以对人声的保留比原有的传统算法做得更好,并且计算实时性可以做得很好,延迟可以做到8ms以内。在对低延时要求非常强的场景下,这个芯片的功耗、延时、算力,目前没有其他芯片可以取代。

另外在做命令词的识别,我们可以去运行AI的算法,可以支持多个语言,并且换词不用重新训练算法,也可以做免换写,最多支持300个词的连续识别。在300个词的连续识别下,芯片的功耗也是低于1mA,包含麦克风的数据处理以及后面识别的功耗。尤其多国语言,要切换语言应用到不同国家的场景下,这个芯片可以很容易做到,而且支持语言是不需要换算法的。

另外在健康领域,它可以做到很低功耗的处理,包括跟PPG、ECG常规的传感器,可以自动地去实时处理,做健康数据的监测,包括血压、血糖、血氧,做运动的识别、做抬腕手势的识别。

对比之前最低功耗的芯片,它的功耗优势基本在6-10倍左右的降低,所以对穿戴类产品,尤其健康场景下常用产品的待机增加幅度是非常大的。

这个芯片也已经有客户用起来做视觉的监测,包括基本的人体检测、物体分类、存在检测等,芯片也可以接轻量级视觉的摄像头,做人体检测还有手势识别的功能。

现在已经使用了WTM2101芯片的产品,包括耳机、模组还有手表,今年预计应该有8个产品差不多可以基于这个芯片实现量产。

四、预告未来五年芯片规划,将拥抱Chiplet生态

除了WTM2101芯片,我们未来也有对存内计算全面的规划,也希望跟大家共同把存内计算的生态推向一个新的阶段。

这是我们的芯片产品规划,2021年是第一代芯片WTM1001,2022年是第二代芯片WTM2101。第一代、第二代芯片的算力提升有接近10倍。

我们在明年会推出8系列芯片,相对第二代的新品算力,预计有800-1000倍的算力提升,算力可以达到几十Tops左右,这个算力已经进行过流片的验证。

我们预计在2025年会推出下一系列C系列的芯片,预计会达到100Tops级别,在2026年会规划更高算力的芯片,当然它的架构还有它的使用材料可能跟现有的8系列、2系列、1系列都会有很大的不同。

这是未来关于知存存内计算产品发展的规划。

除了存内计算的算力,我们更关注在存内计算的工具链、生态的建设。知存的团队正在打造一个最适合存内计算的工具链,更好地开发存内计算产品。

这里面我们总结出来有几个非常重要的部分,做好这3点,才能把存算一体真正用好。

第一,针对存内计算芯片进行算法自动化设计。

现有的深度学习算法很多基于现在CPU,DSP和NPU做了很多优化,这种优化并不适合存内计算芯片,没有把存内计算的优势充分发挥出来,因为存内计算适合大规模并行数据的计算,尽量减少数据的流动。针对存内计算它的架构,芯片的优势怎么自动化设计算法,这是一个很重要的任务要去完成,我们做了一些这方面的事情。

另外我们认为一个很重要的事情,就是存内计算,因为里面是包含模拟的计算,它的计算精度定义跟数字计算不一样。就算模拟计算的精度可以达到非常高,比如一个存储单元可以存10比特,用10比特可以理解成1024个值,用1024个值表示数据电路的1比特、2比特结果也是不一样的。

因为数字信号的1比特、2比特它是绝对的1、绝对的0或绝对的1、2、3、4。即使模拟的精度更高,但它不是绝对的量化值。比如表示1,模拟信号可能是1.001,也可能是0.999,这里面是有差别。模拟的计算精度可以更高,应该更好地被利用起来,这需要新的深度学习训练方法。这个方法或者工具链开发好之后,存内计算的发展速度,它的应用速度、开发速度都会大幅度的提高,可能在客户的开发时间会从原先的1~2个月节省到1~2周。

第二个是架构和工具链。我们现在的芯片是2.0架构,后面会做出Memcore3.0的架构,我们预计新的架构会使用超过5年的时间,它相对来说更通用、可拓展性更强,更稳定、高效。我们8系列、未来的C系列产品,在五年内都会去使用这个新的架构。

此外还有映射的工具,怎么自动化开发算法、自动化训练算法,还有自动化把算法移植到芯片上。最重要的是,这个工具会兼容历史的芯片,意味着我们在老产品当中开发的算法可以直接在新的产品中直接应用,这可以大幅度节省客户开发产品的时间。

第三,在新的技术方面我们也投入了很多,包括在工艺方面,我们持续在研究,未来会有一个更好的存储器件,它更稳定,可以做更多比特的存内计算,在计算能效上也比现有的高出4-8倍。

这里面在工艺上做了很多调整的创新,因为传统的存储器并没有针对存内计算做任何的优化,所以这里面可优化的空间非常多。此外,更高密度的集成,也是未来几年要探索的事情,尝试把存内计算的存储器往更高的三维维度做集成。

最后值得一提的是Chiplet,存内计算也要拥抱Chiplet的生态。我们现在已经在做的事情,包括针对2.5D、3D如何实现跟CPU、跟存储器、跟GPU,在不同工艺来混合兼容,这样可以更好地发挥存内计算的性能。

我认为Chiplet生态,包括先进封装的生态可以把存算一体带到一个新的高度,因为它让存储器的工艺和逻辑工艺以及其他工艺更好,更容易兼容在一起,并且大幅度降低了开发的成本。

这是我今天的报告。谢谢大家。

以上是王绍迪演讲内容的完整整理。