芯东西(公众号:aichip001)

作者 | ZeR0

编辑 | 漠影

芯东西9月10日报道,近日,知名半导体IP和芯片提供商Rambus分享了其进一步扩展的DDR5内存接口芯片组合,发布全新的DDR5 SPD Hub串行检测集线器、温度传感器芯片。

Rambus大中华区总经理苏雷表示,新产品的推出,使得Rambus不仅可以在服务器内存模块市场拓展了产品组合,也为其在消费级内存模块市场开辟了新的机遇。

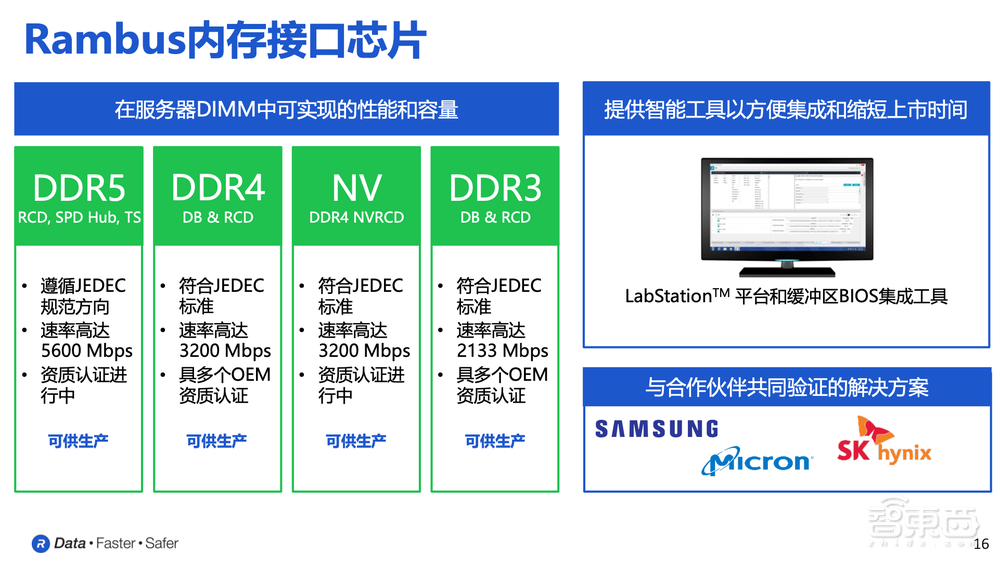

Rambus成立于20世纪90年代,是一家业界领先的半导体IP和芯片提供商,总部位于加州,全球员工有700多名,拥有3000多项专利,在DDR5研发方面历史经验丰富。当前Rambus的主要业务分为基础专利授权、芯片IP授权和内存接口芯片,后续还会推出CXL各产品组合芯片。

Rambus大中华区总经理苏雷、Rambus内存互连芯片业务部门产品营销副总裁John Eble分别发表演讲,深入讲解了内存的六大技术要求,以及其DDR5设计的关键技术创新,并分享了他们所观察的行业发展趋势。

目前Rambus服务的主要市场有数据中心、5G、边缘计算、IoT和自动驾驶等,其中数据中心是Rambus的主要关注点,驱动了大部分的业务增长。苏雷说,Rambus的发展策略是首先通过关注数据中心的各项应用,开发出一系列领先的解决方案,然后逐步向更广泛的市场去推广。

一、关于内存,应考虑的六大技术要求

Rambus内存互连芯片业务部门产品营销副总裁John Eble谈道,关于内存的一些相关标准和需求可以持续5~10年,因此考虑所有的技术要求非常关键。

在John Eble看来,最关键的两大需求就是容量和带宽,两者必须成比例地扩展,这是推动内存子系统设计的最大趋势。

第三点需求是,处理器希望以高速缓存行为单位接收数据,所以内存通道上的内存请求的访问粒度必须保持在64字节。

第四点,数据和数据接口的可靠性必须与现有产品相同或更好,必须支持单错误校正和双错误检测,并有能力在任一DRAM损坏时保存数据。

第五点,扩展服务器性能的关键挑战是将热量从机箱中排出,并且控制温度的能力。为此,DIMM通常被设计为保持在约15瓦的功率运行。

最后,必须控制启动和内存训练的时间,以免影响预期的启动时间。

“这最后三个要求也是我们扩大产品组合,增加两款芯片的主要动机。”John Eble说。

二、补充DDR5 RCD实力,两款芯片新品技术优势详解

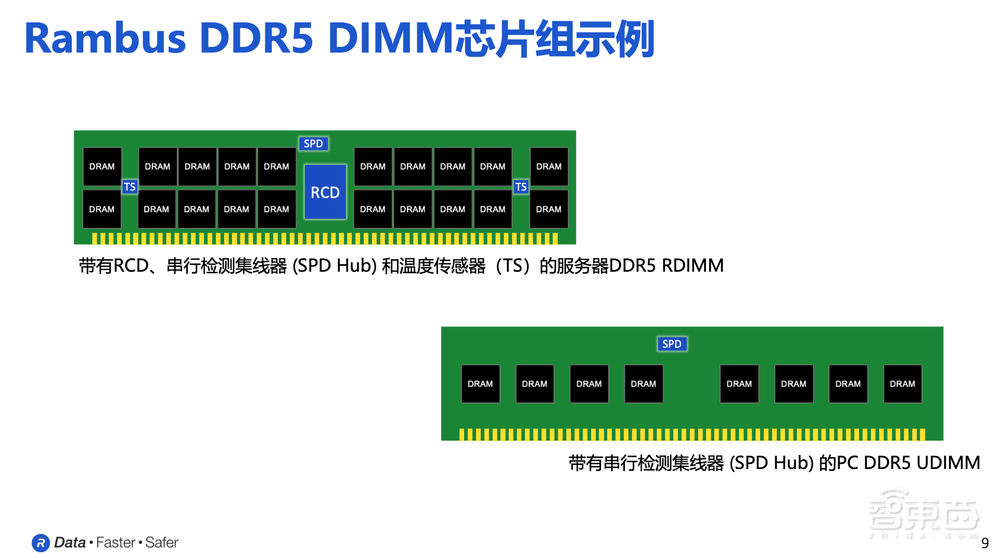

Rambus一直专注于接口芯片的信号完整性。其DDR5系列产品组合的两款新芯片中,串行检测集线器(SPD HUB)是多功能的,是通往DIMM模块的通信网关,温度传感器(TS)则负责在DIMM的不同位置提供高精度的温度信息。

这两款芯片都是对DDR5 RCD的补充,以提供最先进的带宽和容量,对于增强系统管理和热控制至关重要,可以帮助实现高带宽和高容量,同时优化总体拥有成本。

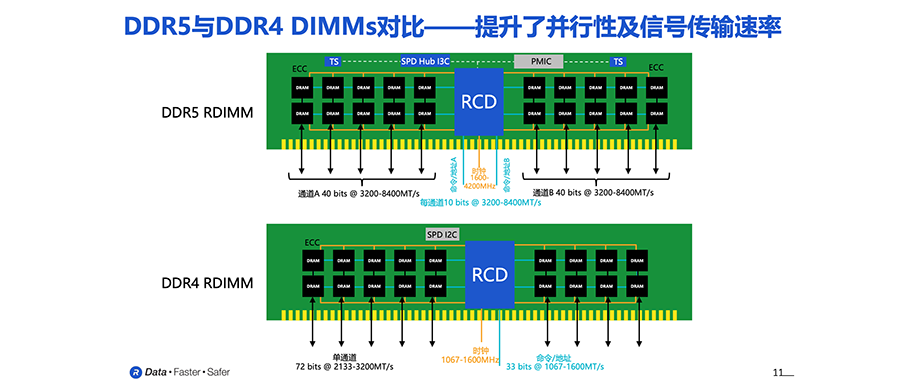

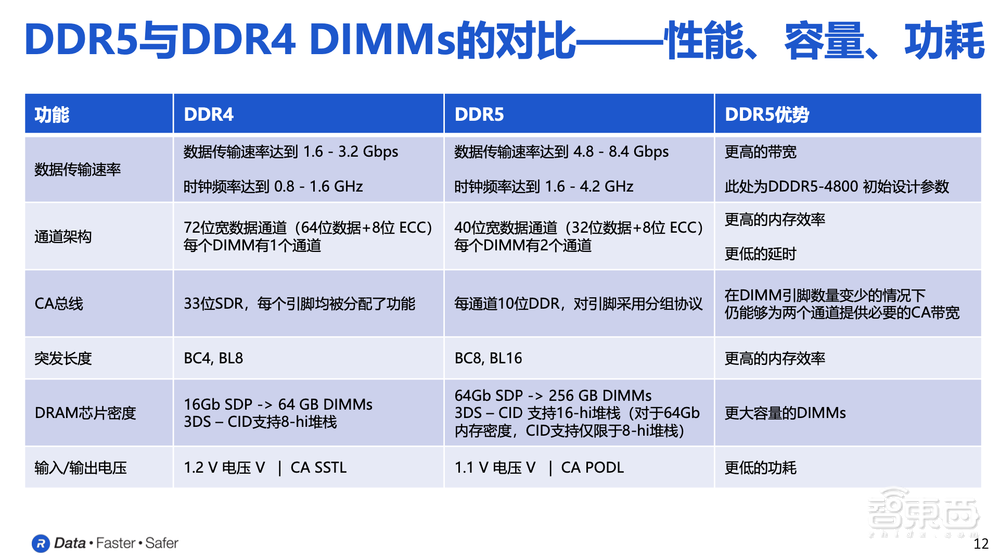

相对于DDR4的设计,Rambus在DDR5模块本身的配置有重大改变。下图对比了DDR5和DDR4 DIMMs的主要区别和优势,包括数据传输速率、通道架构、CA总线、突发长度(BL)等。

这些改变能够保证更大容量、更高的带宽,并降低加载延迟。

DDR4模块采用单一的内存接口通道,具备72位总线,包含64个数据位和8个ECC位;DDR5的通道架构分成两个数据通道,每个通道具备40位宽,包括32个数据位和8个ECC位,以保持相同的ECC保护,并允许存储元数据,每个模块的额外通道不仅满足了访问粒度的要求,而且还增加了内存效率和数据的并发性。

DDR4的突发斩波长度为四,突发长度为八。而DDR5的突发斩波和突发长度将扩展到八和十六,以增加突发有效负载,在突发长度为十六 (BL16)的情况下,允许单个突发访问64字节的数据,这是典型的CPU缓存行大小。

DDR4具有33个特定功能的引脚,运行单一数据速率的时钟。为了在与DDR4相同的模块引脚数下容纳两个独立的命令/地址总线,DDR5为其两个数据通道使用了单个时钟,给每个命令/地址总线分配了10个引脚,每个总线运行双倍数据速率,以进一步提高效率。

在数据通道的原始速度方面,DDR4的最高数据传输速率为每秒3200MT/s,DDR5的起始速率则将达到4800MT/s,其设计的最高数据传输速率将达8400MT/s。

另外,DDR5 DIMM具备更高的相关容量,每颗芯片最大密度从DDR4的16Gb增至DDR5的64Gb。对于使用单芯片封装的DIMM来说,每个模块的最大容量将从64GB增加到256GB。更高容量的DIMM可以通过3D堆叠技术实现。

如果不是从一开始就考虑到功率问题,更高的性能和容量可能会带来更高的功耗。为此,DDR5将工作电压降低到1.1V,命令/地址信号由SSTL改变至PODL, 当引脚停留再高阻状态时,具有无待机功耗的优点。

两款芯片新品的推出,使得Rambus的DDR5 DIMM芯片组更加完整,能够实现更好更高效的内部验证过程,以及更高质量的校验,确保整个芯片达到之前所设计的质量标准或速率标准。

John Eble说,Rambus将这些芯片一起提供给客户后,并为它们的质量负责,客户可以进行自己模组的整合,假如使用途中遇到问题,只需找一家供应商就能解决。“我认为这确实带来了更好的客户体验。”

三、助攻数据中心,降低总体功耗

谈及DDR5的市场应用情况,John Eble分享道,当前DDR5已被应用到不少高端游戏PC,并将拓展至整个PC市场,需要应对计算密集型工作负载的服务器端也对DDR5有着很高的需求。

随着国内新一代环境友好型数据中心逐步建设,服务器对更高的性能、能源效率和其他指标的要求变得更加严格,对下一代服务器内存的需求也与日俱增。

Rambus大中华区总经理苏雷认为,数据中心是全球基础设施的大脑,服务器也正在向着更多的异构计算引擎的方向发展。服务器中部署越来越多的专用芯片,面向特定的任务。在数据中心聚集的技术,最终会扩散到边缘和终端设备。

“可以预期,几乎所有的服务器都会逐渐采用DDR5。接下来的三个月到半年时间,我们预计将看到更多支持DDR5的服务器处理器将会上市。”John Eble说。

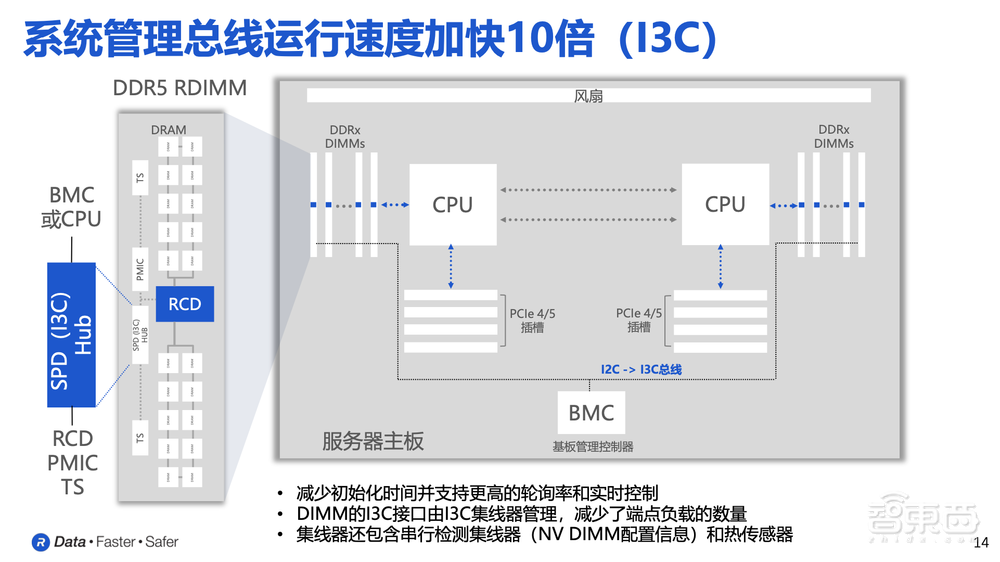

据他分享,一种非常典型的服务器设计是两插槽设计,每个插口都有自己的一组DIMMs和PCIe插槽,可以填充SSD、网卡、加速器等。另外有一个底板管理控制器,可以通过各种接口与主板的所有组件进行通信,最后还有一系列的风扇来管理散热和温度。

额外的DDR5功能,则有助于加强电源传输系统的管理和遥测,从而改善整体服务设计和性能。

系统管理总线在初始化时被大量使用,以发现接入的DIMMs,并执行早期的内存通道校准。过去使用的I2C运行频率约为1MHz,而DDR5平台采用I3C总线,运行频率可达10MHz。

DDR5 DIMM架构为了支持这种更高的速率,通过引入I3C SPD Hub,将总线隔离到控制器一侧的单个DIMM,与主机进行通信。

在目标端点,它可以与模块上其他具有I3C接口的芯片进行通信,包括RCD、PMIC和独立的热传感器。除了减少初始化时间,总线速度的提高也将支持更高的轮询率和实时控制。该集线器还包括串行存在检测集线器,存储了DIMM的非易失性配置信息,并具备热传感器。

两侧的独立温度传感器芯片,通过I3C接口连接到I3C集线器。这为每个DIMM提供了三个空间数据点,提供了关于服务器中温度情况的大量信息。服务器/CPU能够使用该功能管理风扇速度/噪声以及DRAM刷新率来提高性能或保留时间,并且可以作为限制带宽的“最后一招”,可以选择节流带宽,以减少热量。

最后,Rambus经过扩展的DDR5解决方案组合能够提供高达5600MT/s的数据传输速率,并且包括串行检测集线器和温度传感器。

John Eble谈道,Rambus非常重视低功率,在电路设计技术上,在每个存储状态下实现尽可能少地耗散功率,新发布的两个产品将帮助感知和报告服务器或PC中具体的系统配置或热管理的重要数据,这些数据传输回来可以做总体分析判断,进一步降低总体的功耗。

结语:DDR5技术已就绪,预计明年出货量超过DDR4

看向未来,关于DDR5普及的预期,John Eble认为,2022年如果要实现真正全面的DDR5时代,还是相对比较激进的。

据他观察,现阶段能实现DDR5的处理器,包括具体宣布能够实现DDR5平台的数量,仍相对有限。目前DDR4仍然保持着强劲的势头,DDR5则处在早期的爬坡阶段。IDC数据显示,DDR5的出货量超过DDR4,预计会在2023年底发生。

“总体来讲,DDR5的技术已经准备好,已经成熟了。”John Eble说,现在需要等待更多支持DDR5的系统出现,DDR5已经建立了可扩展性,我们将看到主要的CPU公司推出支持性的DDR5,同时增加I/O性能和引进CXL,这些综合技术趋势将使每个插座有更多的内核,提高虚拟化效率,并能够在CPU的低延迟访问中运行具有更大数据集的应用。

从应用的角度来看,他认为随着转向异质计算架构,更多专用加速器将使用定制的内存解决方案,如GDDR或HBM,来优化其性能。

他也看好正在崛起的边缘计算的市场。这同样是Rambus关键的业务领域之一,通过提供全面的芯片产品和IP解决方案,来助力边缘计算行业实现增长和提高安全性。