芯东西(公众号:aichip001)

作者 | 翊含

编辑 | Panken

芯东西3月28日消息,美国AI训练芯片巨头英伟达在本周一发表了一篇技术博客文章,详细解读了该公司新提出的AutoDMP开源方法。该方法能有效地搜索设计空间,找到更好的超大规模集成电路设计宏观布局解决方案。

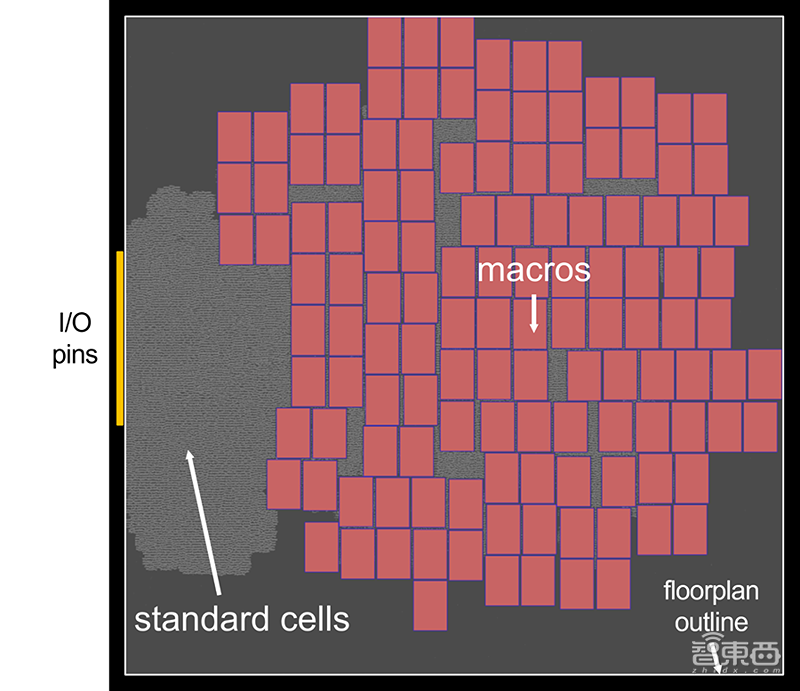

大多数现代数字芯片都以存储块或模拟块的形式集成了大量宏(macro),例如时钟发生器。这些宏通常比标准单元大得多,标准单元是数字设计的基本构建块。

宏布局对芯片的布局有巨大影响,直接影响面积和功耗等许多设计指标。因此,改进这些宏的布局对于优化每个芯片的性能和效率至关重要。

▲芯片平面图显示了英伟达NVDLA分区中标准单元(灰色)和内存宏(红色)之间的巨大尺寸差异(图源:NVIDIA Developer)

传统情况下,设计人员依照惯例会手动进行宏布局。例如,它们可能出现在平面图轮廓的外围。但是手动查找最佳宏布局位置非常耗时。考虑到宏布局、标准单元布局以及由此产生的PPA(功率-性能-面积)之间新型的复杂关系,这一过程可以得到改进。

最近在宏布局方面所做的两项改进为基于强化学习的宏布局以及宏和标准单元的并发布局。

论文链接:https://d1qx31qr3h6wln.cloudfront.net/publications/AutoDMP.pdf

一、用强化学习方法可提高宏布局质量

强化学习方法将宏布局问题表述为游戏,游戏agent(智能体)的动作对应于宏的可能位置。通过对许多布局示例进行采样,agent学习并优化其策略(通常由神经网络表示)以提高宏布局质量。

宏布局质量是根据替代目标(例如线长、拥塞和密度)来估计的。但这些替代目标不是根据实际布局进行评估,而是根据从快速但直接的布局算法获得的标准单元簇的近似布局进行评估,以保持运行时的可管理性。

强化学习方法需要大量的计算。例如,20个GPU和200个CPU用于训练和微调agent的神经网络模型,需要运行10+小时。

二、改进混合布局方法,扩展搜索空间

并发单元和宏布局方法采取混合尺寸布局方法,同时布局宏和标准单元。最先进的混合尺寸布局工具利用数值算法来有效优化选定的目标,如线长和密度。这些工具还可以在目标函数中考虑拥塞和时间,并进行数值优化。这种方法已经在商业EDA工具中实现。

尽管并发单元和宏布局方法取得了较好的结果,但它还可以进一步改进。数值算法有许多算法参数,构成了一个大的设计空间。布局的最终质量取决于选择哪种参数配置,用并发单元和宏布局来扩大这个设计空间,可以进一步增加次优差距。

此外,传统布局算法将多个设计目标合并为一个单一目标进行优化,一个多目标优化框架可以扩展搜索空间并减少优化差距。

这项工作旨在证明,利用基于机器学习的多目标优化和GPU加速的数值布局工具,可以有效地搜索庞大的设计空间,找到更好的宏布局方案。

三、AI+GPU:将全局布局提速约30倍

本文展示了如何使用最先进的开源分析布局器DREAMPlace作为并发宏和单元布局的布局引擎。DREAMPlace将布局问题表述为布局密度约束下的线长优化问题,并对其进行数值求解。线长目标和密度约束都可以表述为可微函数。

线长目标用平滑的log-sum-exp函数近似。密度约束被视为静电系统,由具有快速傅里叶变换的泊松方程求解。DREAMPlace使用PyTorch框架启用的GPU加速算法以数字方式计算线长和密度梯度。它仅在全局布局上就实现了30倍以上的加速。进一步的工作还加速了GPU的精确布局,在CPU实施的工业基准测试中实现了超过16倍的加速。

DREAMPlace支持混合大小布局,即同时布局宏和标准单元格。下图显示了开源设计MemPool的布局过程。

▲优化期间,内存宏和(红色)和标准单元(灰色)一起分布在平面图轮廓内,以在密度约束下最小化导线长度(图源:NVIDIA Developer)

四、增加初始位置和宏光晕参数,扩展宏布局设计空间

作者在DREAMPlace中选择了一组16个参数来定义设计空间,这些参数是根据对布局质量有显著影响的观察结果确定的,包括与优化相关的参数(例如基于梯度的数值优化器及其学习率)和物理参数(例如用于密度评估的箱数和密度目标)。

除了原有的DREAMPlace参数外,还增加了下面列出的参数,以进一步扩展宏布局的设计空间。

初始位置:DREAMPlace最初将单元格和宏的所有初始位置设置在平面图的中心,调整这些初始位置会显著影响最终布局质量。

宏光晕(macro halos):为了简化宏合法化,添加了两个参数以强制宏之间的最小垂直/水平间距。间距约束被转换为在宏周围添加的填充。

▲从中心到右上角修改单元格的初始位置会导致两种最终布局截然不同(图源:NVIDIA Developer)

五、采用多目标优化,寻找高质量宏布局样本

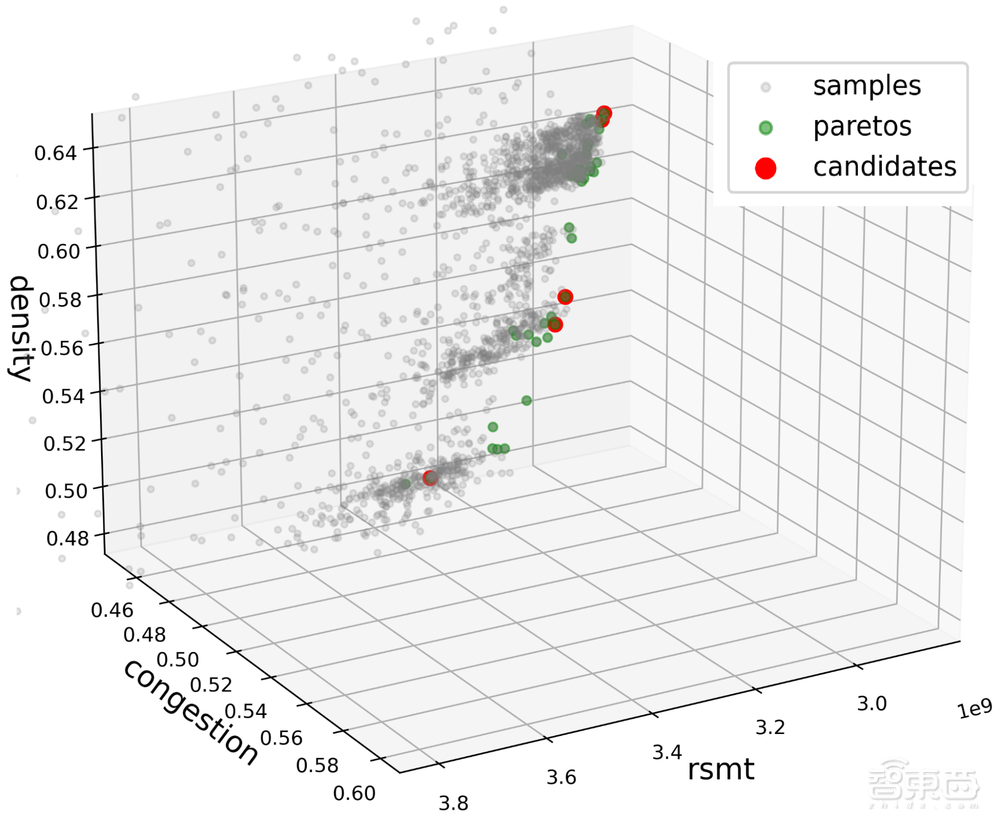

作者建议在参数空间中使用多目标优化而不是单目标优化。目标是线长、密度和拥塞。所有这三个目标都是由DREAMPlace的详细布局来评估的。线长是用直线型斯坦纳最小树(RSMT)的长度来近似。密度是DREAMPlace中使用的目标单元密度。最后,用RUDY算法估计拥挤程度。

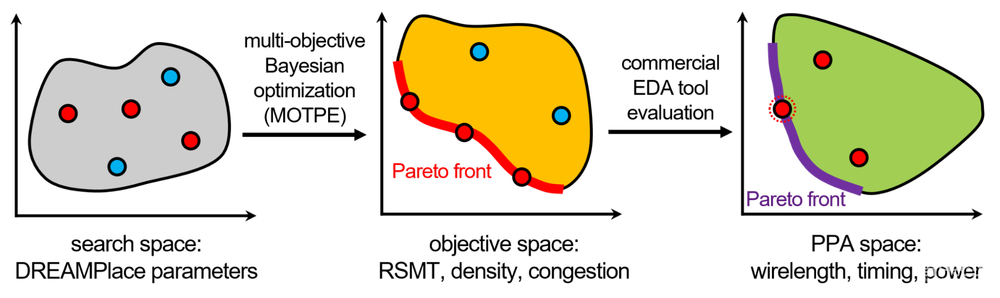

多目标优化寻求找到帕累托前沿,下图是一组非支配性的目标空间点,在这里没有任何目标可以在不降低至少一个其他目标的情况下得到改善。

▲线长、密度和拥塞的三维目标空间。多目标优化通过识别和导航Pareto前沿来寻找高质量的宏观布局样本(图源:NVIDIA Developer)

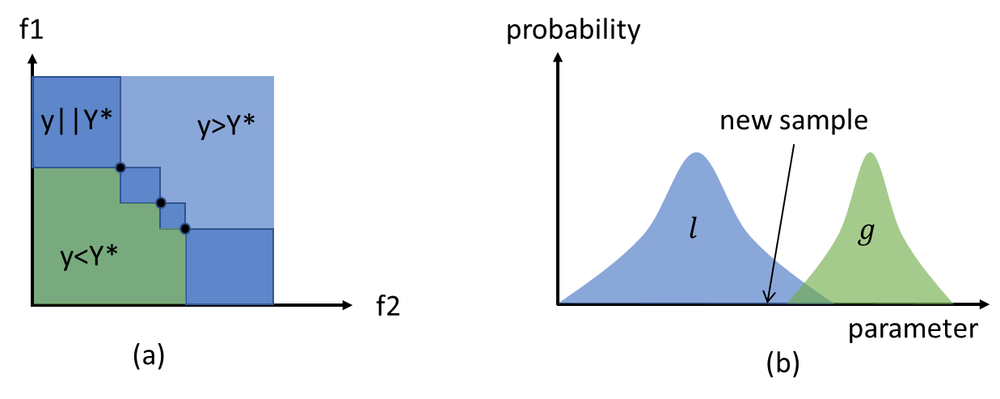

使用多目标树结构Parzen估计器(MOTPE)能有效地搜索Pareto(帕累托)前沿。它基于贝叶斯优化算法,这是一种以学习内部模型作为指导的智能搜索技术。

该模型从先前采样的数据中近似参数配置与目标之间的关系,这有助于为未来的样本找到更好的搜索配置。MOTPE的特殊性是通过基于目标值划分参数空间来模拟给定目标的参数的条件分布。

优化过程如下图所示。在左侧(a),区域由二维目标空间中具有三个样本点的假想Pareto前沿(Y*)定义,绿色区域比Pareto前沿差,蓝色区域包括与当前Pareto前沿相同或更好的点。在右侧(b),两个概率密度函数l和g分别针对蓝色和绿色区域内采样的数据学习,绘制参数的新样本,以便它们可能处于分布l下。

▲MOTPE方法(a)和从Pareto前沿(b)划分空间产生的概率分布(图源:NVIDIA Developer)

与其他单目标优化算法相比,MOTPE很好地支持离散搜索空间。每个参数都有其条件密度,这往往会找到不太依赖于参数交互的良好设置。搜索后可能会发现许多Pareto最优点,这表明布局解决方案具有多样性。

由于反馈延迟要求和共享资源限制(服务器、工具许可证等),在商业电子设计自动化(EDA)工具中评估所有这些点是不切实际的。相反,3D点被聚类以将Pareto点减少到更小的候选集,目标空间中彼此靠近的点对应于看起来相似的位置。

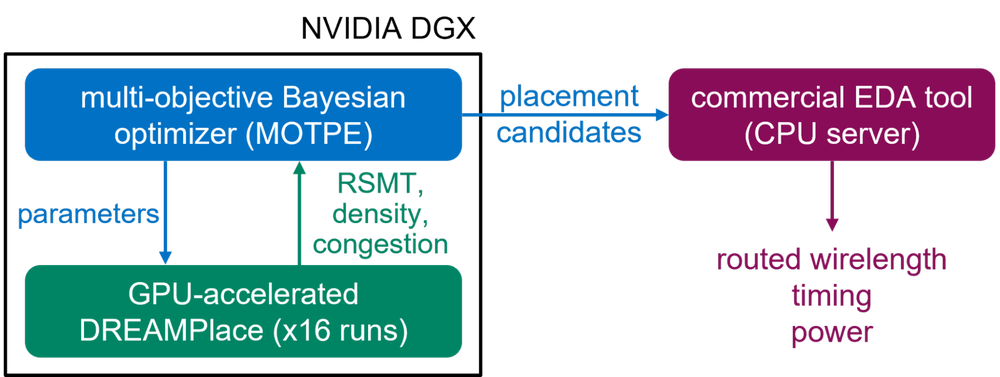

六、两级PPA评估可提升评估效率及结果精确度

作者提出了一种两级PPA评估方法,以减少布局质量估计器与流程结束PPA结果之间的相关性差距。

▲两级PPA评估(图源:NVIDIA Developer)

首先,AutoDMP多目标参数优化找到一组布局,其估计线长、拥塞和密度位于Pareto前沿。此步骤实质上是将AutoDMP参数的设计空间映射到目标代理空间。然后,将目标空间Pareto前沿上的宏布局映射到EDA工具的真实PPA空间。

EDA工具对布局进行了大量优化,故两个Pareto前沿可能不匹配,又因为其中许多是启发式驱动的,因此很难预测映射结果。这就需要在目标代理空间的Pareto前沿对所有宏布局运行EDA工具,并评估实际PPA指标,例如布线长度、时序和从EDA工具流程执行中获得的功率。

为了减少不必要的计算资源使用,应停止流程,尽早评估PPA(例如,在place-opt阶段),并丢弃没有希望的宏布局。

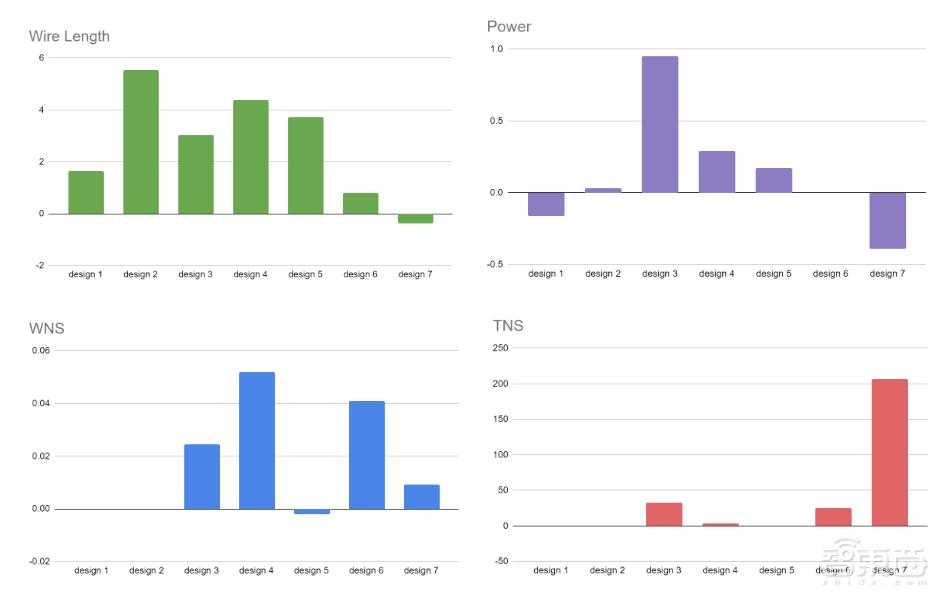

七、结果:PPA指标比肩或超过商用EDA工具

AutoDMP在TILOS AI-Institute提供的宏布局基准上进行评估。该基准测试最初是为了公平地评估Google Circuit Training方法的性能而提出的,它包括一组具有大量宏的CPU和AI加速器设计。为了进行评估,AutoDMP与商用EDA工具集成。

首先,在英伟达DGX系统上运行多目标贝叶斯优化。这个系统有四个A100 GPU,每个都配备了80GB的HBM内存。生成16个并行进程以对参数进行采样并在优化期间运行DREAMPlace。然后,从Pareto前沿选择的宏布局被馈送到TILOS提供的EDA流中,该流在CPU服务器上运行。

▲AutoDMP的计算流程(图源:NVIDIA Developer)

TILOS基准测试包括多种设计,其中一些仅在时序和密度目标方面有所不同。多目标优化对每个设计采样1000个设计点。在单个DGX系统上运行搜索只需几个小时。从Pareto前沿中选择五个宏布局以供EDA流程处理。PPA指标在流程结束时(二次路由)收集。

下图报告了每种设计的这五个宏布局的最佳PPA,所有指标都使用默认的商业宏布局流程结果进行了标准化。在大多数设计中,AutoDMP的PPA指标结果为线长、功率、最差负时序裕量(WNS)和总的负时序裕量(TNS)等于或优于商业流程。

▲AutoDMP在路由后阶段之后的PPA指标相对于商业宏布局结果进行了标准化(图源:NVIDIA Developer)

作者观察到,在一个技术节点(例如NanGate45)的设计中使用AutoDMP实现的最佳参数可以应用于另一个技术节点,例如ASAP7。这表明AutoDMP找到的最佳参数可以在较小的设计更改之间转移。

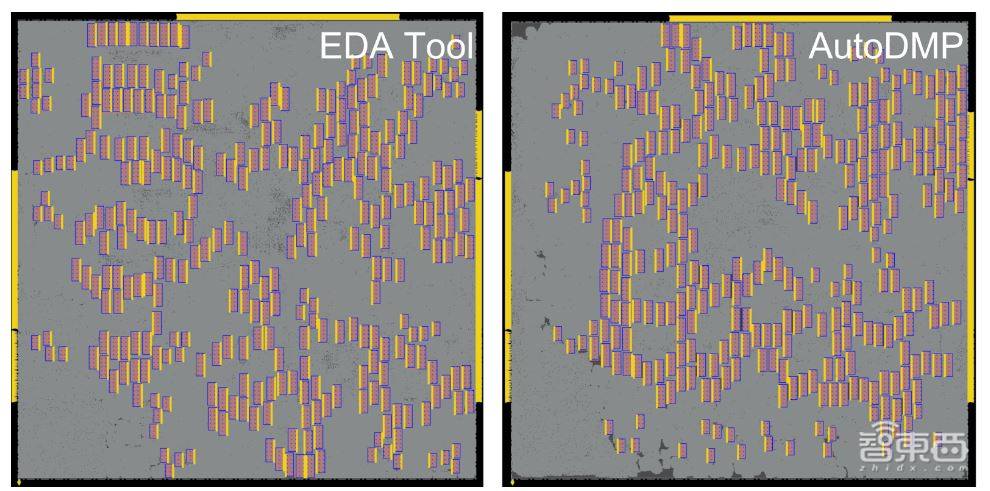

下图显示了最大设计MemPool在基准测试中的位置,它集成了256个RISC-V内核,占270万个标准单元和320个内存宏。经过3.5小时的搜索后,AutoDMP会生成一组宏布局候选。

▲EDA工具和AutoDMP方法论的MemPool设计宏位置(图源:NVIDIA Developer)

结论:英伟达玩起芯片自循环,用AI+GPU加速芯片设计

英伟达提出了一种利用DRAMPlace改进宏布局以达到优化芯片性能和效率的超参数优化技术,即AutoDMP。AutoDMP是一种将宏和标准单元格同时布局在使用多目标的自动参数调整的结合处的超参数优化技术,文中给出了AutoDMP具体的计算方法。

这项工作展示了将GPU加速布局器与人工智能/机器学习多目标参数优化相结合的有效性。鉴于可扩展性在现代芯片设计流程中的重要性,希望这种方法能够解锁新的前瞻性设计空间探索技术。

来源:NVIDIA Developer