芯东西(公众号:aichip001)

作者 | ZeR0

编辑 | 漠影

近日,英特尔实现Intel 3制程节点大规模量产,面向数据中心市场的全新英特尔至强6处理器系列均基于Intel 3打造。相比上一代Intel 4,Intel 3的晶体管密度更高,实现了约0.9倍的逻辑微缩以及17%的每瓦性能提升。

这个重要节点,标志着英特尔雄心勃勃的“四年五个制程节点”计划进入冲刺期,下一个节点迈向“埃米时代”。

多年以来,芯片制程节点的命名不再对应晶体管实际的栅极长度,每家各有一套命名体系已是业界惯例。从2021年起,英特尔正式终结以“nm”来命名起制程的方式,制定了专属于英特尔的命名新规。如今的Intel 3实质上等同于同行的3nm,接下来的Intel 20A、Intel 18A、Intel 14A相当于同行的2nm、1.8nm、1.4nm。

英特尔对EUV(极紫外光刻)技术的运用也更加娴熟,在Intel 3的更多生产工序中增加了对EUV的应用。继Intel 3量产后,同样采用EUV技术Intel 20A和Intel 18A两个节点正在顺利推进中。下一个Intel 14A可能成为英特尔实现巨大飞跃的里程碑节点,这将是英特尔首次使用更先进的High-NA EUV(高数值孔径光刻)技术。

从新品的推出到采用先进的High-NA EUV技术,这方方面面我们不难看到英特尔正稳步推进其“四年五个制程节点”计划,以在2025年重获制程技术领先性。重夺制程领先性,英特尔有诸多“底气”:

第一重底气来自英特尔的执行力。面对AI时代日新月异的算力需求和能效瓶颈,英特尔在技术和产品领域努力突破,并稳步推进路线图。英特尔CEO帕特·基辛格也曾公开表示,英特尔将如期或提前完成其“四年五个制程节点”计划。

近日Intel 3成功实现大规模量产,并应用于新一代领先产品至强6能效核处理器,不仅再次证明了英特尔贯彻执行力推进“四年五个制程节点”,也进一步满足了AI推动下“芯经济”指数级增长的算力需求。现在是时候重新考量英特尔作为制造业领导者的地位了。

第二重底气是在全新GAA晶体管架构、背面供电、先进封装等技术储备方面一马当先。Intel 3之后便进入“埃米时代”,英特尔今年下半年开始生产Intel 20A,明年开始生产Intel 18A。这两个节点都会继续采用传统EUV技术,并应用RibbonFET晶体管和PowerVia背面供电技术。

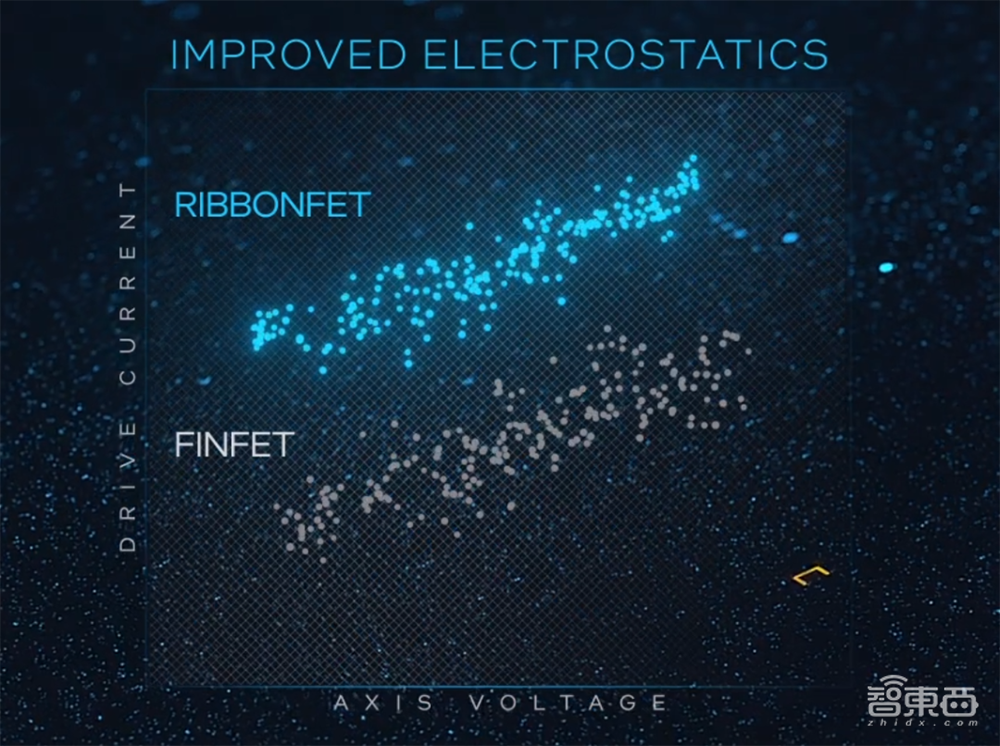

RibbonFET是英特尔首个GAA(全环绕栅极,gate-all-around)节点,也是英特尔自FinFET之后的首个全新晶体管架构,有三大优势:一是让晶体管开关的速度更快,提升晶体管性能;二是水平沟道可垂直堆叠,能提高性能密度,推动晶体管尺寸进一步微缩;三是沟道可根据需求加宽或缩窄,提升了芯片设计的灵活性。

▲英特尔RibbonFET与FinFET晶体管架构对比(图源:英特尔)

▲英特尔RibbonFET与FinFET晶体管架构对比(图源:英特尔)

背面供电同时改善了晶体管供电和信号传输,搭配英特尔全新的散热技术,能够为设备提供更好的性能功耗比。

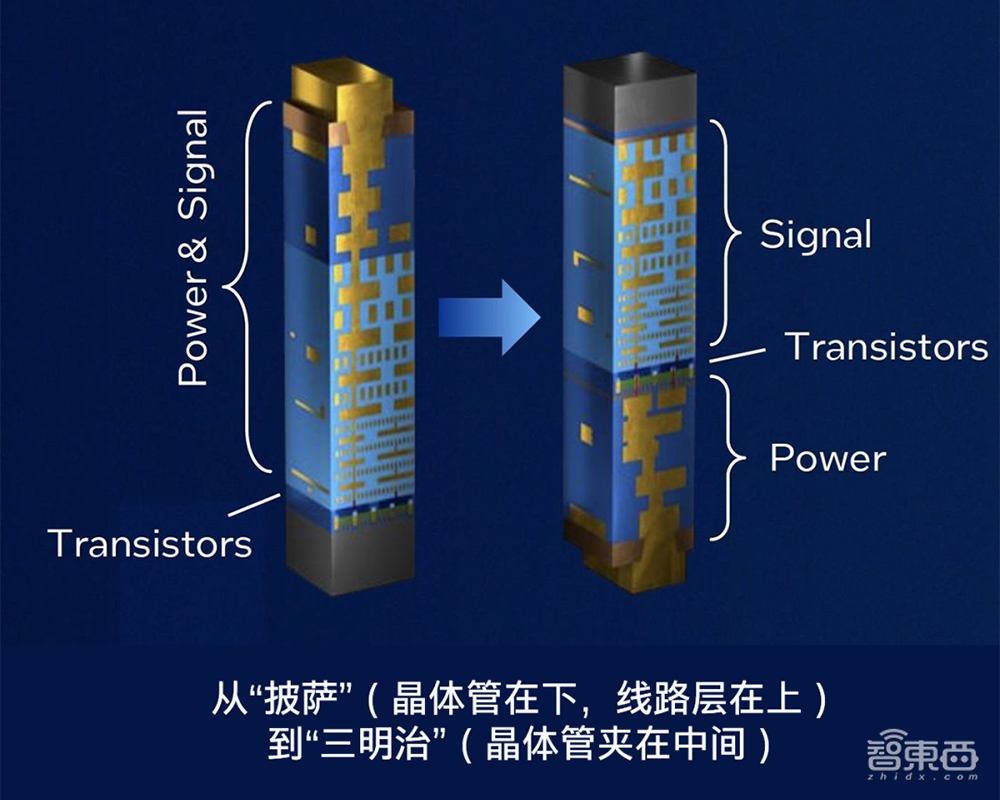

英特尔Intel 18A将向代工外部客户开放,在代工业率先提供PowerVia背面供电解决方案。该方案使用纳米硅通孔连接晶体管,小到只有现有常用硅通孔的1/500,并采用“三明治”结构,将电源线搬到晶圆背面,能改善晶体管供电,减少信号串扰,将平台电压降低优化30%,并解决了晶体管尺寸不断缩小带来的互连瓶颈,实现了6%的频率增益和超过90%的标准单元利用率。

▲传统“披萨”结构与PowerVia“三明治”结构对比(图源:英特尔)

▲传统“披萨”结构与PowerVia“三明治”结构对比(图源:英特尔)

三星、台积电都计划在明年量产的2nm节点采用GAA晶体管架构。三星预计到2027年将其背面供电技术BSPDN用于1.4nm制程。

第三重底气是英特尔面向AI时代打造的系统级代工——英特尔代工(Intel Foundry),将提供从工厂网络到软件的全栈式优化。这被英特尔视作其代工业务在AI时代的差异化优势所在。

英特尔及其生态系统从晶体管、互连、先进封装到系统架构、软件、应用程序等方面的系统级协同优化,将确保满足各种不同需求。它计划通过Intel 14A节点进一步提供High-NA EUV、第二代RibbonFET晶体管、第二代PowerVia背面供电、先进封装等领先技术的组合。

为了持续推进摩尔定律,实现2030在单个封装内集成1万亿个晶体管的目标,英特尔还在探索如何超越RibbonFET,通过仅三个原子厚的超薄2D材料技术变更,在单个芯片上集成更多晶体管。

第四重底气是采用High-NA EUV光刻技术。

作为首家大规模采用High-NA EUV光刻技术的公司,英特尔将推动整个行业向更高端的制造工艺迈进。英特尔率先采用High-NA EUV光刻技术,这不仅标志着其在芯片制造技术上的一次重大飞跃,更预示着英特尔在半导体行业将占据先机。这项技术将使英特尔能够生产出更小、更快、更高效的2nm及以下节点芯片,从而在市场中赢得优势。

随着芯片制程的不断缩小,英特尔将能够降低生产成本,同时提升产品的性能和可靠性,这将增强其产品的市场竞争力。此外,英特尔在High-NA EUV技术领域的领先地位,将使其在晶圆厂工具生态系统中发挥引领作用,其技术要求和标准可能成为行业新的标杆。

结语

Intel 3的成功量产标志着英特尔正稳步推进“四年五个制程节点”计划,并且为即将到来的“埃米时代”奠定了基础。通过不断提升晶体管密度、引入先进的High-NA EUV光刻技术,英特尔展示了其强大的技术储备和执行力,距离2025年重回制程领先地位的目标越来越近。

面对AI时代日益增长的算力需求,英特尔不仅在技术层面持续创新,还在代工业务和系统级优化上发力,力求全方位满足市场需求。尤其是RibbonFET晶体管架构和PowerVia背面供电技术的引入,使得英特尔在晶体管性能、密度和设计灵活性上实现了重大突破。

身为摩尔定律的头号代言人,英特尔有义务,也必须成为那个义无反顾挑战物理极限的先行者。随着Intel 20A、Intel 18A和Intel 14A节点的推进,英特尔正通过层层加码的四重底气,坚定不移地推动摩尔定律的进一步延续。面对后摩尔时代的新命题,这些冲在技术创新最前线的不竭探索、对生态建设与产业链升级的不吝投资,终将推动硅基革命的车轮滚滚向前。