芯东西(公众号:aichip001)

作者 | ZeR0

编辑 | 漠影

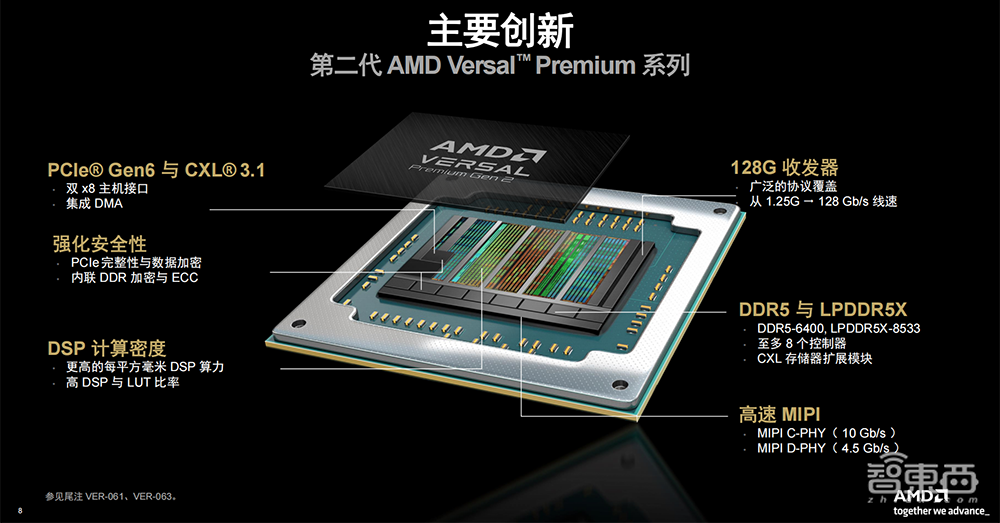

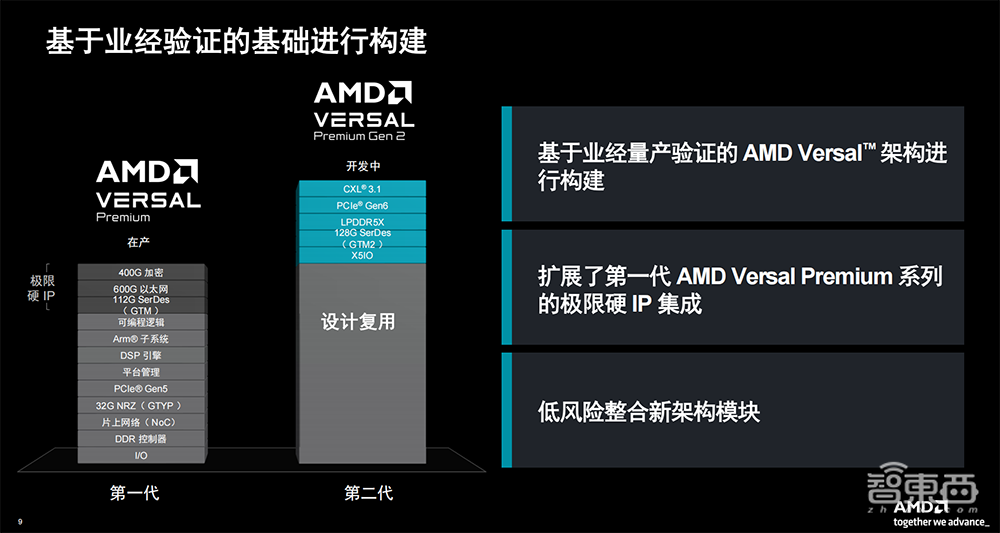

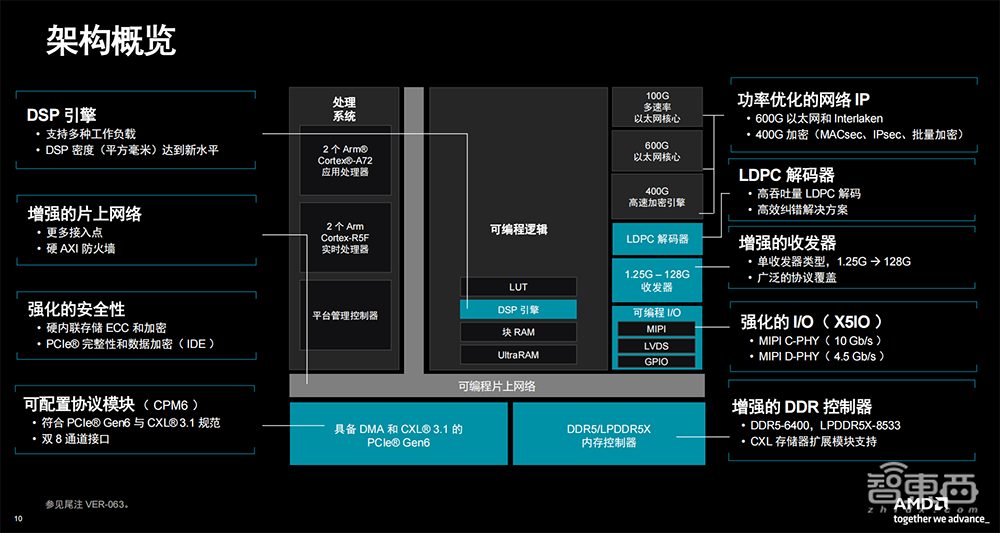

芯东西11月13日报道,AMD昨日宣布推出全新自适应SoC平台第二代AMD Versal Premium系列,旨在面向各种工作负载提供最高水平系统加速。该系列采用6nm制程,将成为FPGA行业首款在硬IP中采用Compute Express Link(CXL)3.11与PCIe Gen6并支持LPDDR5存储器的器件。

相比第一代产品,第二代AMD Versal Premium系列有三大创新:一是加速主机连接,二是更快释放更多内存,三是增强数据安全性。

这些下一代接口和存储器技术能在处理器和加速器之间快速且高效地访问和迁移数据。CXL 3.1和LPDDR5X可助力更快速地释放更多内存,以满足数据中心、通信以及测试测量市场中数据密集型应用日益增长的实时处理和存储需求。

新自适应SoC平台还实现了更高的每平方毫米DSP算力,引入了一个新收发器GTM2,支持1.25~128Gb/s数据速率、NRZ和PAM4编码,效率最高可达7pJ/bit。

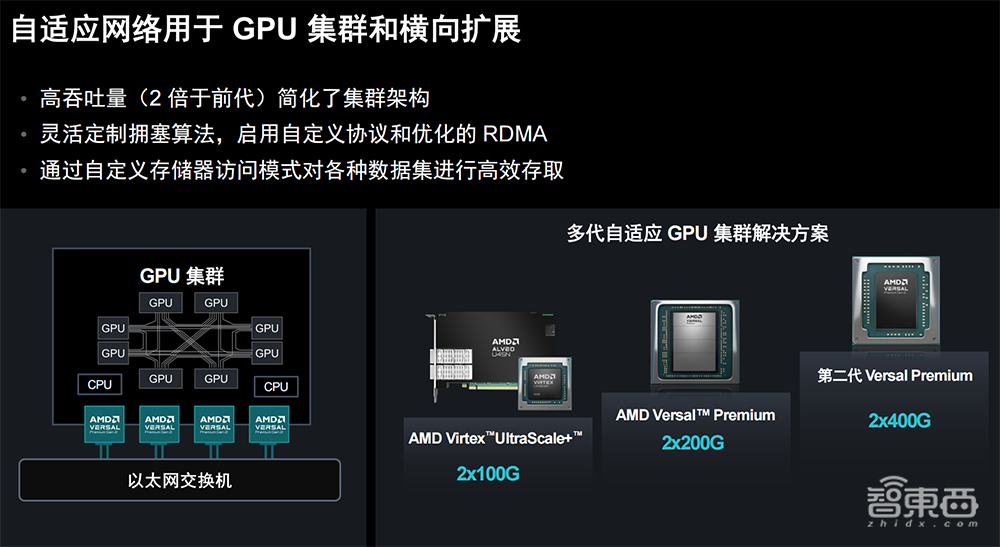

该系列能够提供很高的带宽和灵活性,可在单个网络适配器上支持2个400G接口。

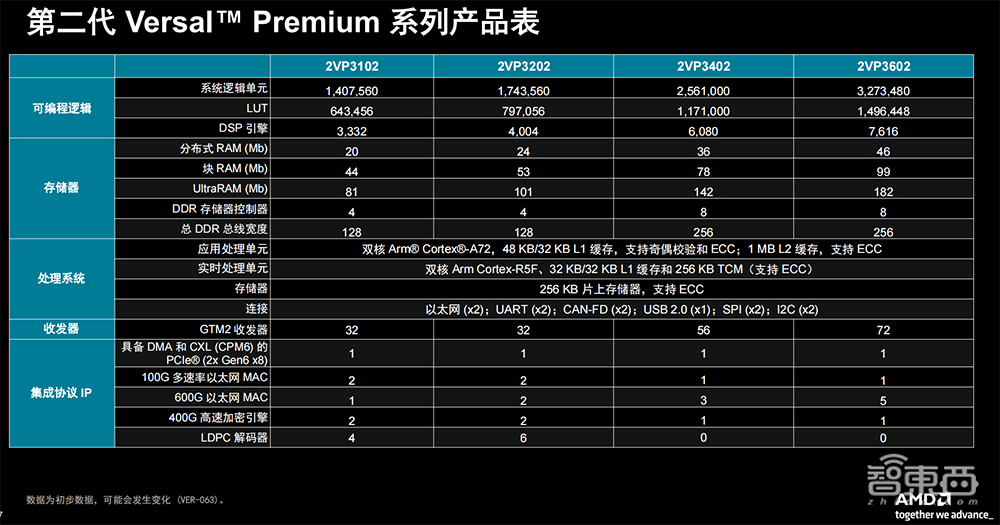

第二代AMD Versal Premium系列共有4种产品,早期文档自今年11月起提供,开发工具预计将于明年提供,于2026年上半年提供芯片样片,在2026年下半年开始量产出货。

一、加速主机连接:支持CXL 3.1和PCIe Gen6

CXL是处理器与器件(如基于FPGA的加速器)之间的开放式行业标准互连技术。据市场研究机构统计,现在出货的近半数服务器已支持CXL。

第二代Versal Premium器件支持业界最快的主机接口CXL 3.1和PCIe Gen6,能够实现行业领先的高带宽主机CPU到加速器连接。

LDPC解码器的模块适用于高通量的解码。

与支持PCIe Gen4或Gen5的FPGA相比,PCIe Gen6可提供了2~4倍的线速率。运行PCIe Gen6的CXL 3.1在类似时延下,能提供使用CXL 2.1器件的2倍带宽,以及增强的架构和一致性功能。

此外,通过将第二代Versal Premium系列搭配AMD EPYC CPU,系统架构师能够利用经CXL或PCIe连接到高性能CPU的最新AMD FPGA的器件,以加速数据密集型应用并满足快速的数据增长需求。

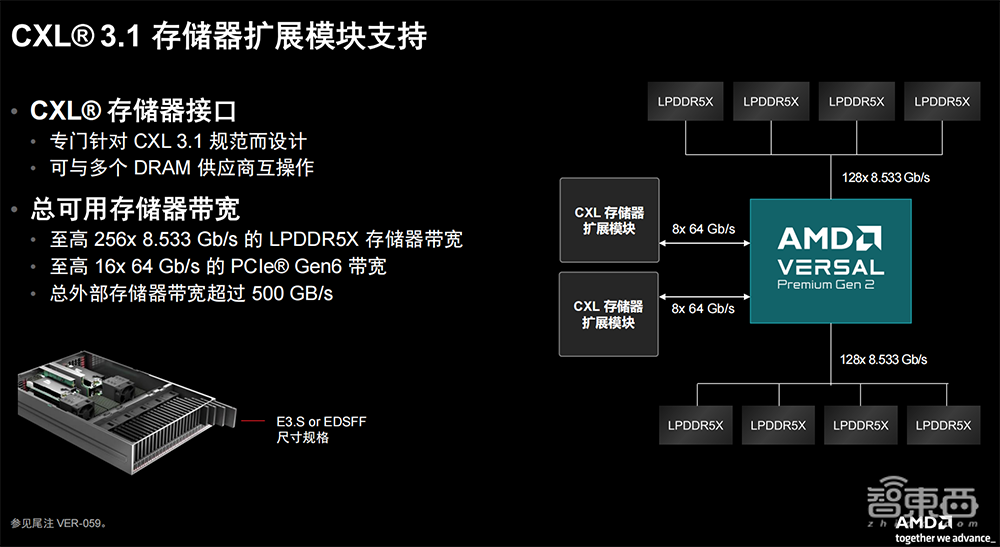

操作模式方面,Versal Premium支持CXL.io、CXL.mem、CXL.cache,器件模式方面可作为内存控制器,还可以使用主机模式,连接CXL存储器扩展模块。

比如使用2个8通道CXL连接,带宽最高64Gb/s,通过这样的架构,总外部存储器带宽可超过500GB/s。

CXL还能提供内存一致性的额外益处,有助于实现真正的异构加速计算。

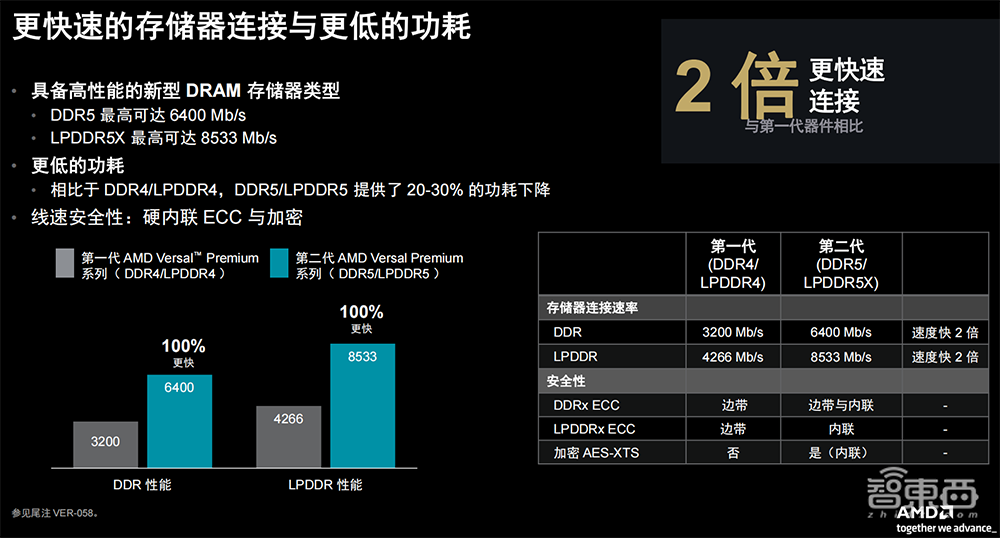

二、提高存储器带宽及利用率:升级DDR5/LPDDR5,连接速度较上一代翻倍

DDR5已经成为行业主流趋势。第二代AMD Versal Premium系列自适应SoC的DDR5连接速率最高达到6400Mb/s、LPDDR5连接速率最高达到8533Mb/s,带来更快速的数据传输和实时响应。

与采用LPDDR4/5存储器的同类器件相比,这种超快的增强型DDR存储器可将主机连接速度提升至高2.7倍。

与CXL存储器扩展模块进行连接,可使总带宽较之单独使用LPDDR5X存储器高出至多2.7倍。因此第二代Versal Premium系列允许为多个加速器实现可扩展的内存池和扩展,进而优化存储器利用率并增加带宽和容量。

通过为多个器件动态分配内存池,第二代Versal Premium系列自适应SoC旨在提高多头单逻辑器件(MH-SLD)的存储器利用率,使其无需架构或交换机即可运行,同时支持至多两个CXL主机。

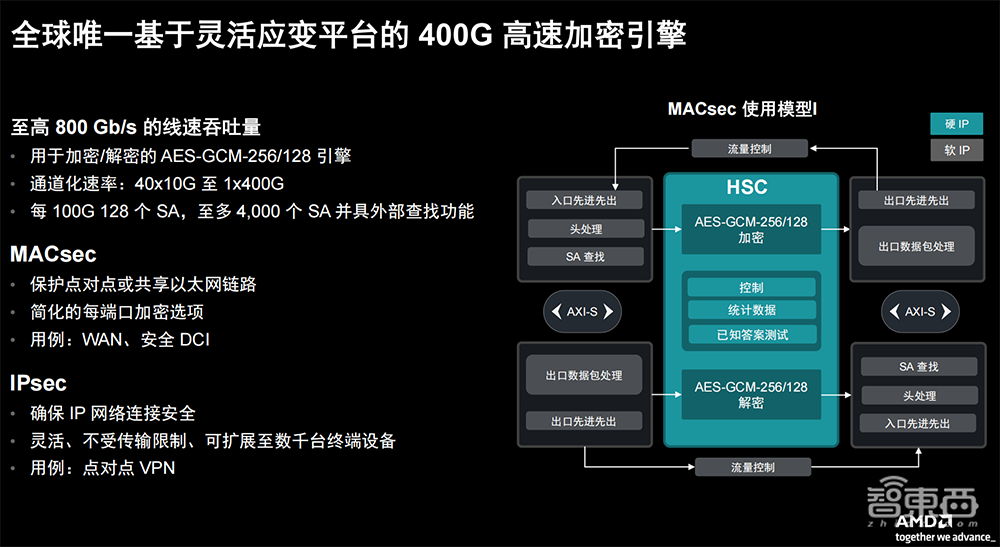

三、加强数据安全:IDE、DDR加密、400G高速加密引擎

增强的安全功能有助于第二代Versal Premium系列在传输和静态状态下均可快速、安全地传输数据。这是业界首款在硬IP中提供集成PCIe完整性和数据加密(IDE)支持的FPGA器件。

硬核DDR内存控制器内置的内联加密可助力保护静态数据,400G高速加密引擎则能帮助器件以至高2倍的线速率保护用户数据,从而实现更快速的安全数据事务。

第二代Versal Premium系列还增加了硬内联ECC与加密来保护内存。

结语:提升整体系统吞吐量,优化存储器资源利用率

相比ASIC,自适应SoC的优点在于可以重新编程来适应新的功能,无需重复工程费用。AMD Versal系列产品一贯针对一些关键应用进行精准设计,来确保能够有最合适的关于算力、I/O以及内存的组合,实现最高性价比。

总体看来,第二代AMD Versal Premium系列的主机连接变得更快,从PCIe Gen5升级到PCIe Gen 6,并采用CXL 3.1规范;内存连接速率提升,从LPDDR4/DDR4升级到LPDDR5X/DDR5,还有CXL存储器扩展模块;通过IDE、DDR加密和400G高速加密引擎,确保数据安全性;另外也增加了内存控制器、LDPC解码器和DSP的能力,还有支持128Gb/s的GTM2收发器。

更快地释放更多内存、更好地管理系统内存,都是当前AI模型及各种数据集成所需要的。此外Versal Premium也能与AMD EPYC CPU之间形成 协同,中间有高性能连接,可共享内存空间,再加上PCIe IDE和内存DRAM的加密,做到端到端数据安全性。

AMD级副总裁兼自适应和嵌入式计算事业部总经理Salil Raje认为:“第二代Versal产品组合的最新成员可帮助客户提升整体系统吞吐量和存储器资源利用率,以实现更高性能,并为从云到边缘的最严苛应用提供洞察。”