智东西(公众号:zhidxcom)

文 | 心缘

3月15日,上海,由智东西主办、AWE 和极果联合主办的 GTIC 2019 全球 AI 芯片创新峰会成功举办!峰会现场延续上一届的火爆场景,全场从开幕到下午结束座无虚席,而且有不少热情观众坚持站着听完峰会全程。

20位海内外 AI 芯片业界大咖齐聚一堂,围绕 AI 芯片在架构创新、生态构建、场景落地等方面的技术前景和产业趋势“华山论剑”。

本届峰会报名参会的观众覆盖了近4500家企业,到会观众极为专业,其中总监以上级别占比超过62%,现场实际到会人数超过1800位。

▲Cadence全球 AI 研发中心高级 AI 研发总监丁渭滨

传统的芯片设计非常复杂,需要具有丰富经验的尖端工程师带领众多精英人才进行长期的设计验证工作,过程中还面临大量不确定情况。作为全球三大电子系统设计自动化(EDA)软件巨头之一,Cadence 早早跻身于人工智能的洪流之中,以机器学习优化芯片设计工具等方式为 AI 芯片产业的发展提供助力。

在 GTIC 2019 峰会上,Cadence 全球 AI 研发中心高级 AI 研发总监丁渭滨带来主题为《应用机器学习进一步提升芯片物质设计的性能》的演讲,分享了 Cadence 在机器学习方面软件工具所做的实际工作和成绩,还预告了两款新工具的正式发布时间。

丁渭滨从工具方的角度阐述了 AI 的两个主要目的,一是利用 AI 做更智能的芯片设计工具,二是实现以更少的人力、资源、周期来设计芯片。

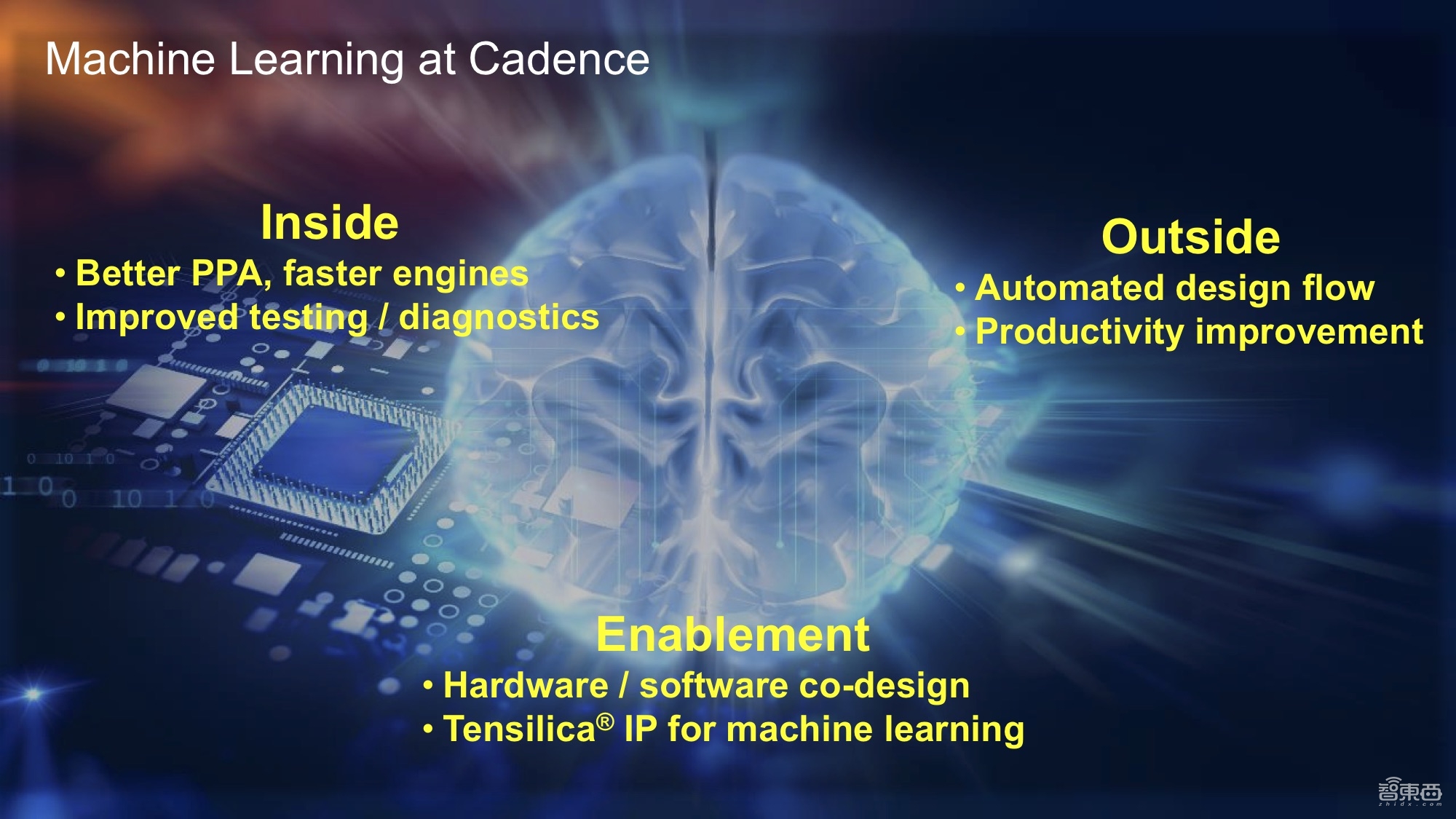

在机器学习领域,Cadence 分别从 Inside 和 Outside 两部分进行定位。Inside 注重于工具本身,力图让工具更智能,使得用户获得更好的 PPA 和更快的引擎,从而提升测试和诊断性能表现;Outside 则注重于人,让机器通过学习的方式积累经验,减少人工干预,极大地释放生产力。

经过历史上几十年的积累,Cadence 拥有广泛的客户基础,并在数字领域形成一套从前端到后端的完整工具链,包含 Project Virtus、Signoff Timing、SmartLEC等工具。

其中有一款布局布线工具 Innovus ,Cadence 在其中内置机器学习算法来取代传统的算法,通过对大量芯片设计数据进行学习建立了一个可自动辅助芯片设计的机器学习模型,完成集成参数的提取、快速布线和运算等方面的工作,已经帮一些用户实现了芯片设计的性能优化。

针对 Outside,Cadence 打造了一款突破性的 Design Flow 专家系统,能通过训练让其进行自我学习、自我进步,不断获得更高的胜率和回报率,最终帮助工程师分担一部分工作。

丁渭滨表示,新版 Innovus 工具将在今年4月份正式发布,另外 Cadence 会在今年10月正式发布一个 AI 自动修正 ECU 芯片设计的软件,目前内部测试中其效果已经比肩有经验的工程师。

附 Cadence 公司全球 AI 研发中心高级 AI 研发总监丁渭滨演讲实录

丁渭滨:大家下午好!

今天有很多收获,很高兴和大家分享一下 Cadence 在机器学习上的投入和成绩。Cadence 是一家提供 EDA 设计软件和 IP 方案的公司,今天我主要谈的是软件工具方面。从工具方来讲,人工智能(AI)有两个最主要的目的:

1、怎么用工具来设计芯片?

假设有一个工程师设计了4个芯片,他的经验得到了很大的提升,他会知道怎么处理很多事情,但工具本身并没有变的更加聪明。所以这是有问题的地方,而我们的工作就是利用 AI 去进化工具。

2、如何降低对芯片人才经验的依赖?

如今设计芯片时,需要非常多的人力和资源。AI 是否可以做到不需要人来设计芯片?或者需要人来干预设计的过程变的越来越少?如果这一目标实现,将极大地释放出生产力,以更少的代价、更快的周期来生产芯片。

机器学习本身有60年的历史,经过了很长一段的冬天,在最近几年突然热起来了,主要原因是它终于开始在安防监控、人脸识别、语音识别、翻译等一些领域成功落地了。

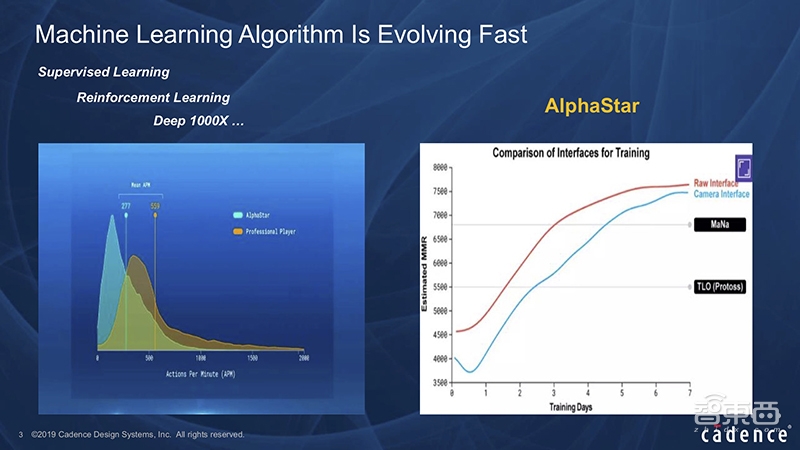

这引起了人们极大的兴趣,特别是当谷歌的《星际争霸》例子出现。在自学了《星际争霸》几百万部、几十万部视频后,机器真的可以看着屏幕来玩游戏,还真的可以打败最顶尖的人类高手。

分享给大家一个很有趣的数据。当我一开始看到消息时,第一感觉是机器的优势来源于它操作鼠标各方面比较快。其实后来谷歌给的报告显示,AI软件在每分钟操作鼠标的次数只有277次,而人类高手高达了500多次。

计算机远远可以比人操作鼠标更快,但是它并没有靠此来赢人类,而是做了更好的决策,它真的知道什么时候做什么决策能得到较高的最终回报。

芯片工程师每天做事情主要是看layout,然后来决定这个时候需要进行什么样的修改,修改完以后预期会解决什么问题。实际上玩游戏不会带来实际的生产价值,而做一颗芯片会带来实际的价值,这就是Cadence在做的事情。

Cadence第一个定位的角度是 Machine Learning Inside 。Inside 注重于工具本身,这是因为今天的工具并不是最完善的。当做一个芯片有很长的设计流程时,用户每一步都在丢失一些东西,因为每一步的算法都在适合优化某些东西,可是这个东西不一定对,不确定每个阶段是否真的往同一方向走。

对不确定性的东西来说,机器学习具有非常大的威力,可以帮助我们得到更好的、更收敛的 Flow,在每个步骤不会浪费不必要的资源。换句话说,当你在设计芯片的时候,很多时候在不确定时会加一些Margin,其实每一次加的时候都是对性能资源的浪费和伤害。机器学习技术很适合于解决这一类问题,利用这一技术,Cadence 让工具变的更聪明,当你运行几次、十几次甚至更多次后,你会发现,工具本身变得越来越好。

另一个角度是 Machine Learning Outside,这个角度是致力于人。因为就算有了 EDA 工具,设计一个芯片仍是非常复杂的事,需要很高的门槛、很强的前端团队和后端团队,即便这样也不一定有用。很多时候要考虑的问题是,当涉及到运行工具、运行 Flow 等各种各样的修正时,你需要这些人做什么?这些人到底在做什么?我们可不可以通过学习的方式减少人工干预?

假设有几百个工程师,每个人每天都学到了不一样的东西,可能在某些点上变的越来越有经验,可是这种经验是非常分散的,分散到每个人的脑子里,并且每个人在他的一生里能做到的 PPA 数量是有限的。

可是如果我们能把这些事情交给机器,机器可以看到和累积所有人的经验,然后变的越来越稳定时,就摆脱了在很多地方对经验的依赖。如果到了这个阶段,芯片设计就走向了另外一个高度、另一个新的天地。

在美国国防部上有一个叫 DAPRA 的项目,其中有一项叫无人设计芯片,Cadence 也有参与这个概念。Cadence在 EDA 公司里拿到了最大的一笔投资,那笔投资试图解决的是 Analog 方面的问题,当你画 PLL 的时候希望把各式各样的经验累积起来,最后不再依赖一定要有非常厉害的人才能画出来。当然,在数字电路同样有这样的事情,人类在探索用 AI 提高生产率上有非常长的路要走,但总的来说,这些都是非常有前景的。

第三个,因为Cadence本身也提供 IP,所以也有 AI 芯片,但今天主要谈工具,就不多谈了。

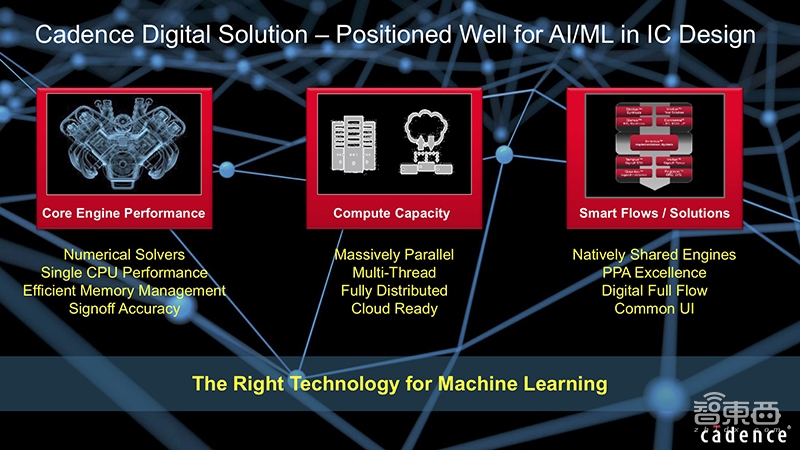

当你要有 AI 来解决芯片设计的时候,你要有基础的东西,首先要拥有已经完整的工具链,只有这样才会有很完整的数据,才能够看到全局。

从这个角度来说,Cadence 是非常有利的,我们有完整的工具链、广泛的客户基础,所以真正可以跟客户一起整合已经有的优势,以达到更好的性能,或者更高的效率。

Cadence 经过历史上几十年的积累,在数字领域有一套完整的前端到后端的设计工具、验证工具,这对人工智能和机器学习来说是很大的财富,因为不可能靠一个工具来做人工智能,到后面工具的世界已经远远地超出了你的认知范畴。

在工具里,Cadence 已有哪些东西可以直接使用呢?一个是在座很多人可能都有用过的 Innovus,这是一款布局布线工具,里面已有内置的 AI 算法取代传统的算法,这个工具在今年4月份会正式发布;另外有一个是 Project Virtus,通过机器学习解决 EM-IR 和 Timing 之间的相互影响;还有 Signoff Timing 和 SmartLEC等工具。

接下来,我给一个更具体的例子帮助大家理解 Cadence 到底做了哪些实际的工作,而不只是在纸上谈这些目标。

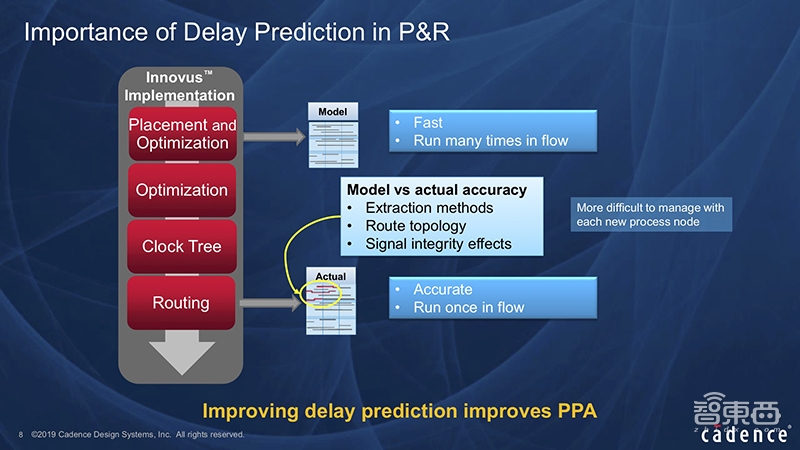

Routing 是一个非常关键的步骤,需要很长时间来运算,才能得到最终结果。随着基础厂商的规则变得越来越复杂,从 7nm 到 5nm 再到 3nm,运行的时间会相比线性增强非常多,这会造成一个问题,当你在前端 Routing 之前做了很多优化,和你在 Routing 之后看到的东西就会截然不同。

不同人会有不同的策略。有的人说既然这样,我在布线之前做的更加多一点,留一些 Margin,这样到后面我的跳变会少一点,所以我的芯片性能还在,这样虽然没错,但往往会浪费很多资源。即便你多做,你也未必知道该在哪里多做;还有一种策略是在某些地方做调整,在某些地方不要去做,其实这无非就是乱枪打鸟,或者是等着天上掉馅饼。

其实这都不是最好的解决方案,机器学习有一个最大的特点,如果结果是基于统计学来看是不确定的,但它整体上又有一个趋势,是由某几百个或者更多的特征来决定,那么它就是一个很适合用机器学习解决的问题。

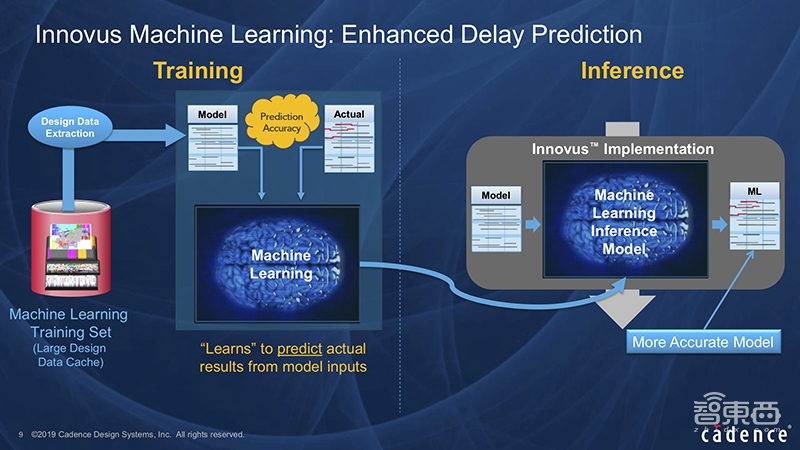

虽然布线非常复杂,可是里面是不是有某种趋势性的东西,我通过运行芯片设计后可以知道?如果可以知道的话,是不是可以训练模型,在布线之前就预测布线完后的时序(Timing)会是什么样的状态?

如果做到这一点的话,基本就把问题解决一半了,只需要在优化器里嵌入这些东西,不要用现在的方法预估来做,用机器学习的方法会比你更准,会优化到真正需要优化的地方,在你布线之后,你会看到你不仅没有浪费,并且性能会更好。

在训练完以后,Cadence 把某模型嵌入到 Innovus 工具中,这个工具依赖于机器学习模型来做 Timing 的计算,而不是像现在传统的方式去做一些集成参数的提取、快速布线和运算。如果花了那么多时间,最后得到的结果还不是想要的,那么我们为什么不用一种更聪明的方式来做?

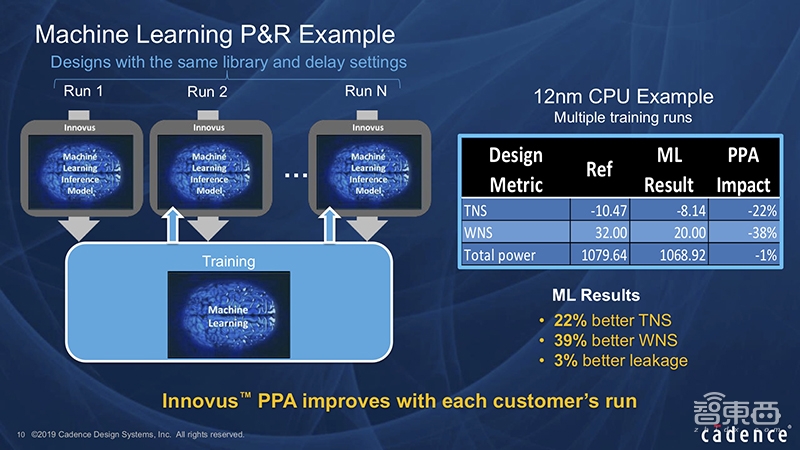

如图是真实的客户数据。该客户是做中低端手机的,他们在做芯片时,PPA 和功耗遇到了瓶颈。为了得到数据,他们之前花了很多工程师的力量做了23组不同的 run。其实实际数据远远超过23组,但这23组是最后得到的有效数据。

既然已经花了这么多工程师和 CPU 得到这个结果,我们帮你把这些东西全部收集起来以训练模型,训练好模型后,他们用我的模型继续优化,真的看到有超过22%的 TNS 和39%的 WNS 的提高,并且更有趣的是发现功效也降了3%。这说明什么呢?说明我在提升性能的时候,没有浪费你的资源。相反因为我做的更好更对,我还帮你节省了资源。

还有一个最近才发生的例子,有一个非常大的手机厂商,主要做比较高端的手机 CPU 芯片。他们原来想要做到 2.8GHz 的频率,可是做到 2.6GHz 的时候就做不下去了,因为工程师花了半年的时间都没有修下去。后来我们花了一个月的时间把以前 run 的结果都收集起来,大概有10个左右有效结果,放在一起花了3到5天的时间做训练,得到模型重新 run。

这时好玩的事情发生了,一开始我们可以帮他们将频率缩短 2.8GHz,后来他们说需不需要冲击一下更高的 3.0GHz 频率?我们又把它调到 3.0GHz 频率,还将功耗省了3.7%左右。他们非常激动,因为对他们来说,如果手机芯片提升了400兆频率,他们在市场上的竞争率不知道增加多少。另外,时间的有效性也得到大大提升,因为只要把数据放上去,不需要投入几十个工程师去调试,工具就会全部自动完成。

我举的例子是这几个月真实发生的事情,得到一个基本的结论就是,把机器学习应用到芯片设计场景里,不是虚幻的事,而是真的可以解决工程问题。只是以前因为数据规模、算法、算力各方面没有能够做到这一点,现在通过 Cadence 的工作可以发现这是真实可实现的。

我们在想怎么可以做更多。工具变好了,是否还是需要这么多人力和时间才可以得到我最后的芯片?或者还可能面临这个问题,有经验的设计工程师走了,把很多知识和想法都一并带走了,新来的人接不上,这个项目可能就不行了。

那么,有没有某种方式把设计的相关知识和经验留在公司里?也就是说,就算有人员流动,你关键知识和数据还在,只要找一个人进来管理好你的数据,就能继续进行芯片设计。

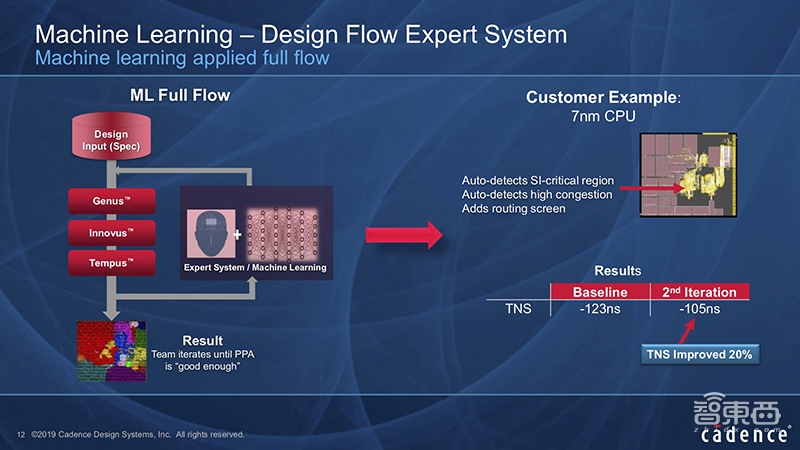

这是 Cadence 提的另一个概念—— Design Flow 专家系统。可能听起来专家系统有点老套,比如很多年前机器人看病问一堆问题, 不像是能真正能解决问题的东西。

其实这个要看怎么做,专家系统概念本身并没有什么不对的地方,关键在于这个专家系统能否做到自我学习。假设它能实现自我学习,那用户就无需担心一开始的专家系统里的知识是不是最好的知识。

这就是 Cadence 做的一个突破,即随着训练慢慢可以让专家系统自我学习、自我进步。想象一下,当 AlphaGo 在下棋的时候,最主要的是预测价值链的神经网络,价值网络可以根据以往自学的经验判断这个时候的胜率回报率到底有多高,最后总是能走到胜率回报率比较高的地方。

做 Design Flow 的设置一定是对应某个可以衡量的指标的回报,假设我们可以把价值回报链做好做完整,其实它是完全可以放在工程师日常工作中,分担一部分工程师的工作。这就是我们讲的 Machine Learning Outside 的概念。

今年10月份,Cadence 会正式发布一个 AI 自动修正 ECU 芯片设计(Timing ECU Fixing)的软件工具。我们已经在内部让跟非常有经验的 PE 工程师来修正,修正的结果并不比工程师差,而且会比他更有效率,因为你可以让机器24小时不断在学习和修正。这才是真正人工智能有威力和带给我们希望的地方,因为没有一个人像他们一样24小时在学,学几十年,学那么快,带给我们最大的惊喜应该是在这里。

今天我的分享就到这里,谢谢大家!