生成式AI时代,大模型及AIGC的快速发展推动着计算需求的高速增长。AI大模型与各个赛道的结合,带来了新的体验革新,这些新体验的落地则离不开各类AI芯片的支撑。放眼全球,产业格局的激烈变动,也让更多中国AI芯片企业看到了新的发展机会。如今各路AI芯片创企可谓是百家争鸣,群雄逐鹿成为国内AI芯片产业的主基调。在这样的产业背景下,我们将全球顶级AI芯片产学研用及投融资领域专家们聚集起来,为他们提供思想交锋、观点碰撞的平台。

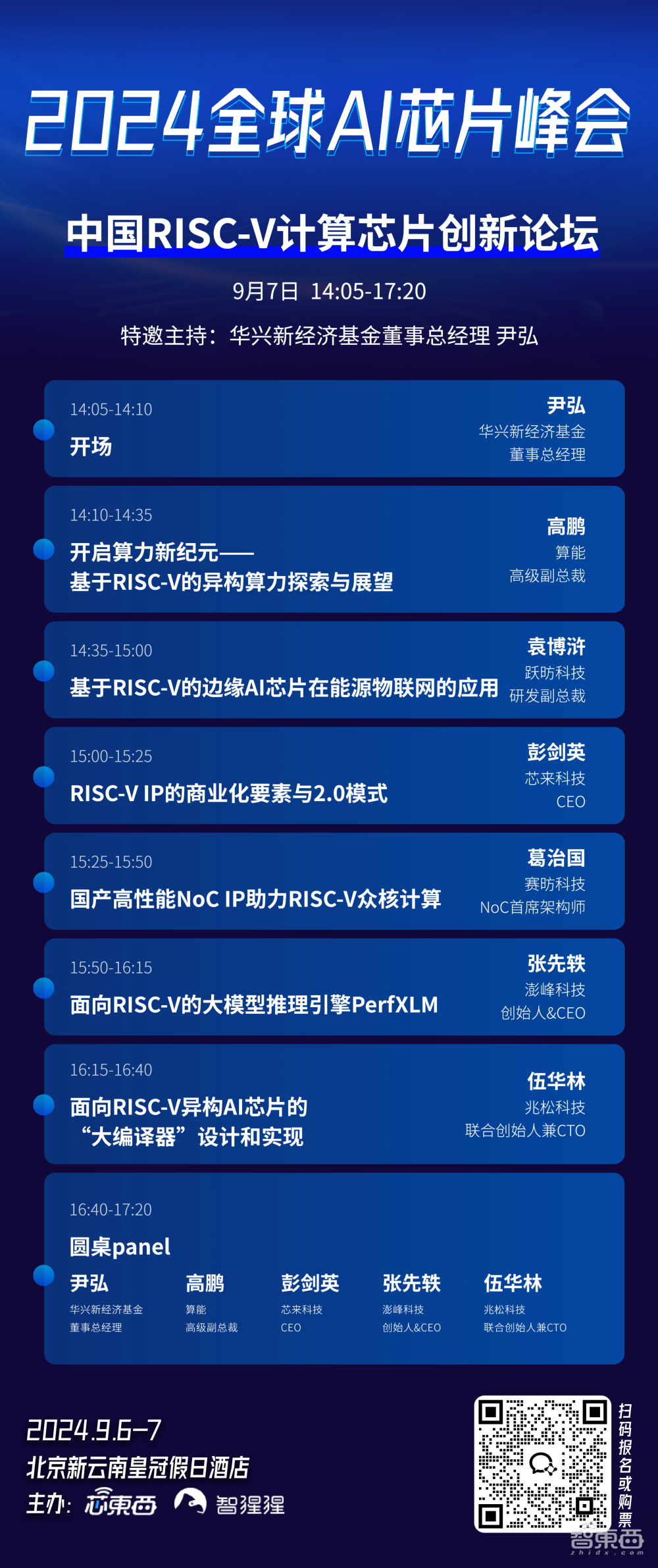

9月6-7日,2024全球AI芯片峰会(GACS 2024)将在北京新云南皇冠假日酒店盛大举办。全球AI芯片峰会至今已成功举办六届,现已成为国内规模最大、规格最高、影响力最强的产业峰会之一。

本届峰会由芯东西与智猩猩共同主办,以「智算纪元 共筑芯路」为主题。峰会采用“主会议+技术论坛+展览展示”的全新形式。主会议由一场开幕式,以及数据中心AI芯片、AI芯片架构创新、边缘/端侧AI芯片三场专场会议组成,将在主会场进行;技术论坛分为Chiplet关键技术论坛、智算集群技术论坛和中国RISC-V计算芯片创新论坛,将在分会场进行。同时,在大会第二天上午的AI芯片架构创新专场结束后,将重磅揭晓两大AIIP AI生产力创新先锋企业榜单,分别是2024年度中国智算集群解决方案企业TOP 20、2024年度中国AI芯片新锐企业TOP 10。

其中,中国RISC-V计算芯片创新论坛将从异构计算、边缘AI芯片、IP商业化要素与模式创新、片上网络NoC、大模型推理引擎和编译器等维度,深入探讨RISC-V产业生态的最新进展和技术创新。

本次论坛邀请到华兴新经济基金董事总经理尹弘、算能高级副总裁高鹏、跃昉科技研发副总裁袁博浒、芯来科技CEO彭剑英、赛昉科技NoC首席架构师葛治国、澎峰科技创始人&CEO张先轶、兆松科技联合创始人兼CTO伍华林7位嘉宾参与,为我们带来主题演讲和圆桌Panel。华兴新经济基金董事总经理尹弘将担任论坛主持人。

人工智能正在逐步成为最重要的生产力要素,如何为高速增长的人工智能计算需求提供高性价比和高能效比的算力是当下研究热点。RISC-V因为自由开放和共识统一的特点使其有希望成为支持通用算力和包含人工智能在内的各种异构算力的统一架构平台。算能高级副总裁高鹏将以《开启算力新纪元—— 基于RISC-V的异构算力探索与展望》为主题,分享算能基于RISC-V架构在处理器领域的技术探索路径。

目前,RISC-V芯片的应用大多集中在工业控制、物联网等对算力要求不高的领域,AI实际应用落地较少。如何加快AI应用落地是RISC-V产业玩家需要共同解决的问题。跃昉科技经过对能源互联网场景需求的深刻分析,推出业界首款基于RISC-V架构的高端边缘智能应用处理器NB2,并构建了从芯片到系统的整体解决方案,目前已实现商业化应用。在本次论坛上,跃昉科技研发副总裁袁博浒将围绕《基于RISC-V的边缘AI芯片在能源物联网的应用》这一主题,分享跃昉科技边缘端AI芯片在能源互联网场景的实践经验。

芯来科技作为本土RISC-V领域的代表性企业,公司CEO彭剑英受邀参与此次论坛,并将以《RISC-V IP的商业化要素与2.0模式》为主题,深入探讨RISC-V生态发展的商业化要素、RISC-V CPU IP 的产业价值、发展趋势与协同创新。

NoC通过高效的片上网络通信架构,能够为多核处理器提供高并行性、灵活性和可扩展性,优化数据传输效率和通信带宽,是现代SoC设计中的关键技术。赛昉科技致力于国产RISC-V CPU IP和一致性片上网络(NoC)IP的自主研发,其一致性NoC IP已成功研发至第二代,专为支撑RISC-V众核的高性能计算而设计。在本次论坛上,赛昉科技NoC首席架构师葛治国将以《国产高性能NoC IP助力RISC-V众核计算》为主题,深入探讨赛昉科技Starlink-700 NoC IP的架构特点和设计理念。

PerfXLM是澎峰科技自研的大模型推理引擎,旨在为各种主流模型提供快速适配多种异构硬件的解決方案。在此次论坛上,澎峰科技创始人&CEO张先轶将分享PerfXLM在RISC-V ISA领域的移植与优化,主题为《面向RISC-V的大模型推理引擎PerfXLM》。

如何快速适配各类AI框架,支持各类模型高效的运行,以及让用户轻松编写高性能的算子库,是一款AI芯片能否得到市场认可的必要条件。为解决AI芯片软件栈和算子库的性能和维护等难题,兆松科技提出“大编译器”的概念。在此次论坛上,兆松科技联合创始人&CTO伍华林将围绕《面向RISC-V异构AI芯片的“大编译器”设计和实现》这一主题,分享如何通过“大编译器”来解决AI模型到异构系统端到端高效适配的问题。

主题演讲环节结束后的圆桌Panel,将由主持人华兴新经济基金董事总经理尹弘、算能高级副总裁高鹏、芯来科技CEO彭剑英、澎峰科技创始人&CEO张先轶,以及兆松科技联合创始人兼CTO伍华林一起带来。

中国RISC-V计算芯片创新论坛将在峰会第二日下午举办,感兴趣的朋友可以扫描底部论坛议程海报上的二维码,添加小助手雪梨申请门票。

一、嘉宾及演讲内容介绍

1、算能高级副总裁 高鹏

高鹏,北京算能科技有限公司高级副总裁,深耕IC设计19年,智算和中大规模处理器设计领域专家,持有10余项发明专利,是国内智算和RISC-V处理器领域最早期的探索者和践行者。

自加入算能以来,成功主导了智算处理器算能BM1684、BM1684X的研发与商用;目前负责算能新一代桌面级处理器产品定义和研发。

演讲主题:《开启算力新纪元—— 基于RISC-V的异构算力探索与展望》

内容概要:人工智能正在逐步成为最重要的生产力要素,如何为高速增长的人工智能计算需求提供高性价比和高能效比的算力是当下研究热点,RISC-V因为自由开放和共识统一的特点使其有希望成为支持通用算力和包含人工智能在内的各种异构算力的统一架构平台。

本次演讲,将分享算能以人工智能应用为主要目标,基于RISC-V架构的处理器领域的技术探索路径,分享算能在服务器级通用处理器、面向大模型应用的边缘智能处理器、面向视觉应用的终端智能处理器方向的产品成果和生态进展,并展望面向智能个人电脑和边缘服务器的重要产品规划。

2、跃昉科技研发副总裁 袁博浒

袁博浒,广东跃昉科技有限公司研发副总裁,具有18年半导体研发及管理经验,专注于SOC、数通类芯片及系统应用技术。曾任赛昉科技高级总监、中国信科/烽火产品总监,熟悉从市场战略到销售管理的全流程产品周期,负责跃昉科技整体研发工作。

演讲主题:《基于RISC-V的边缘AI芯片在能源物联网的应用》

内容概要:目前,RISC-V芯片的应用集中在在工业控制、物联网、智能家居等对算力要求不高的领域,AI实际应用落地较少。基于对能源互联网场景的深刻分析,跃昉科技推出业界首款基于RISC-V架构的高端边缘智能应用处理器NB2,并构建了从芯片到系统的整体解决方案,已成功在能源互联网场景实现商业化应用。

本报告将分享跃昉科技针对能源互联网应用场景的需求分析、解决方案和实践经验以及未来演进方向。

3、芯来科技CEO 彭剑英

彭剑英,芯来科技CEO,浙江大学博士,15年以上处理器设计和相关管理经验。曾任Synopsys ARC处理器高级研发经理并建立ARC处理器中国研发中心;曾任Marvell ARM处理器验证经理等。

作为芯来科技创始人之一,彭剑英结合自身的技术优势和管理经验,统筹芯来科技整体运营、市场营销、产品研发和产业生态构建,在其带领下,公司整体运营呈现飞速发展的良好态势。

同时担任RISC-V中国产业联盟秘书长、浙江大学微电子学院研究员、中国移动物联网联盟理事会理事,并荣获2023上海创业先锋前10强。

演讲主题:《RISC-V IP的商业化要素与2.0模式》

内容概要:本次演讲,将对RISC-V生态发展的关键商业化要素进行分析,并深入探讨RISC-V CPU IP 的产业价值、发展趋势与协同创新。

4、赛昉科技NoC首席架构师 葛治国

葛治国,赛昉科技NoC(Network On Chip) 首席架构师,新加坡国立大学博士,有着15年以上芯片设计经验。在知名学术会议发表多篇文章,并获多项美国和国际专利。

曾在华为作为核心成员参与自研一致性协议、NoC和可配置加速器等多个项目研发。加入赛昉科技以来,领导自研两代一致性NoC。

演讲主题:《国产高性能NoC IP助力RISC-V众核计算》

内容概要:一致性片上网络(NoC)IP作为高性能计算领域的核心技术之一,广泛应用于数据中心、专用处理器(DPU)、人工智能(AI)芯片等场景。作为构建高效、安全、可持续AI生态系统的基础,NoC IP提升了系统的整体性能,降低整体能耗,进一步推动了人工智能技术的发展和应用。赛昉科技作为专注高性能RISC-V IP和软件解决方案厂商,始终致力于国产RISC-V CPU IP和一致性片上网络(NoC)IP的自主研发,其一致性NoC IP已成功研发至第二代——昉·星链-700(Starlink-700),专为支撑RISC-V众核的高性能计算而设计,为其提供强劲的内核动力。

本报告将深入探讨赛昉科技Starlink-700的架构和设计理念,包括其设计特性、多样化应用场景以及未来演进方向。

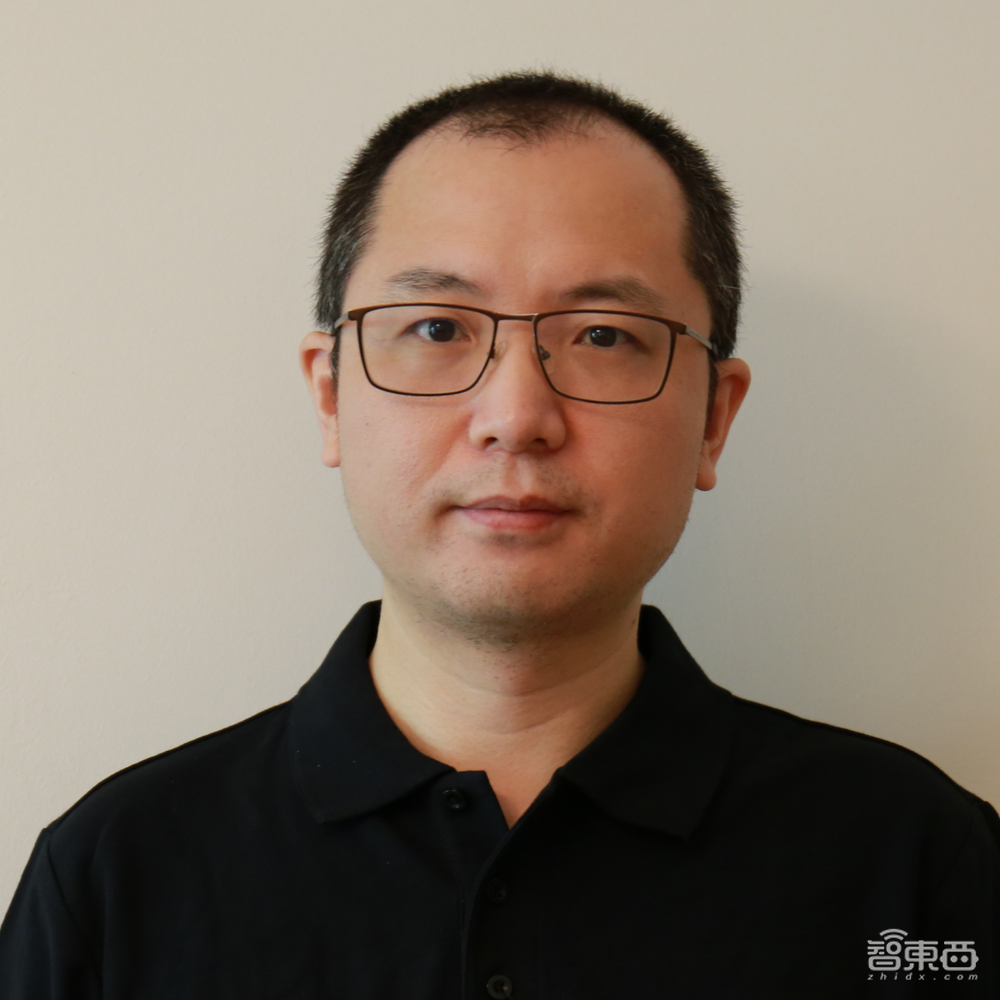

5、澎峰科技创始人&CEO 张先轶

张先轶,澎峰科技创始人&CEO,本科和硕士毕业于北京理工大学,博士毕业于中国科学院大学,曾于中科院软件所工作,之后分别在UT Austin和MIT进行博士后研究工作。国际知名开源矩阵计算项目OpenBLAS发起人和主要维护者。中国计算机学会高性能计算专业委员会执行委员,ACM SIGHPC China执行委员。2016年,创办PerfXLab澎峰科技,提供异构计算软件栈与解决方案。2016年获得中国计算机学会科学技术二等奖,2017年获得中国科学院杰出科技成就奖,2020年 美国SIAM Activity Group on Supercomputing最佳论文奖,2023年北京市自然科学二等奖。

演讲主题:《面向RISC-V的大模型推理引擎PerfXLM》

内容概要:本次演讲,将介绍澎峰自研的PerfXLM大模型推理引擎,以及PerfXCloud大模型开发与部署平台,并探讨GenAI算力需求急剧增长背景下,新兴的RISC-V ISA在此领域的移植与优化。

6、兆松科技联合创始人兼CTO 伍华林

伍华林,兆松科技联合创始人兼CTO,曾就职于Andes、S3、Imagination编译器部门,参与和负责CPU、GPU、GPGPU芯片的编译器等设计和研发,拥有十多年编译器行业从业经验。 于2019年和前Andes软件部门VP王东华一起创办兆松科技。

演讲主题:《面向RISC-V异构AI芯片的“大编译器”设计和实现》

内容概要:如何快速适配各类AI框架,支持各类模型高效的运行,以及让用户轻松编写高性能的算子库,成为一款AI芯片能否得到市场认可的必要条件。 同时,进一步降低AI芯片的软件栈研发成本和算子库维护成本,提升硬件利用率,也成为AI芯片公司走向盈利的必经之路。

兆松科技为解决AI芯片软件栈和算子库的性能和维护等难题,提出了“大编译器”的概念。传统编译器只针对某一特定指令集的芯片产生单线程或者多线程的可执行文件,兆松科技基于MLIR框架设计的“大编译器”,支持PyTorch, Tensorflow, ONNX, JAX导入,结合Triton和Mojo(未来支持)等类Python语言编写的高层次算子库,在统一的MLIR多层中间方言实现全局的图优化以及更优的算子融合策略,从而进一步提升AI芯片的效率。同时,“大编译器”还对平台相关的runtime进行了平台无关的抽象,从而实现从控制器代码自动生成、AI加速器代码自动生成、控制器和AI加速器数据搬运代码自动生成的功能;并且因为只需要维护一套和平台无关的高层次算子库(平台相关的内容自动由编译器产生),让算子库的维护变得更加简单。

兆松科技设计的这套“大编译器”在第一阶段支持基于RISC-V架构的AI芯片(包括数据流芯片),未来会逐步扩展支持非RISC-V架构的AI芯片。

本次演讲主要分享兆松科技是如何通过“大编译器”来解决AI模型到异构系统端到端高效适配的问题。

二、论坛完整议程